# Overview of Algorithmic Methods in IC Reverse Engineering

#### Leonid Azriel

Technion

- IC Reverse Engineering in a nutshell

- Scan-based netlist extraction

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Summary and Future Directions

#### **Ethics of Reverse Engineering**

- Semiconductor Chip Protection Act (US) 1984 allows reverse engineering of commercial semiconductor products for educational purposes

- Ethical goals

- Detect vulnerabilities that allow reverse engineering and propose countermeasures

- Explore legitimate usages of the reverse engineering for defense

- Hardware Trojans detection

- IP theft detection

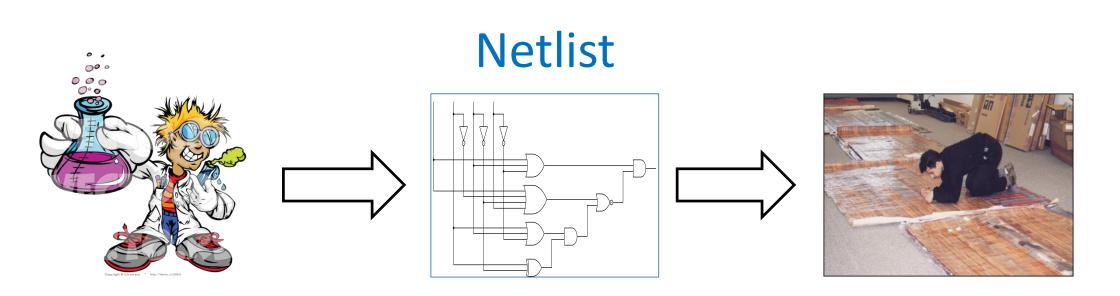

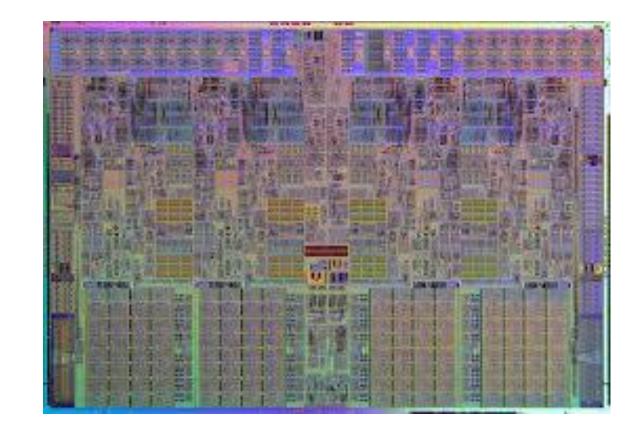

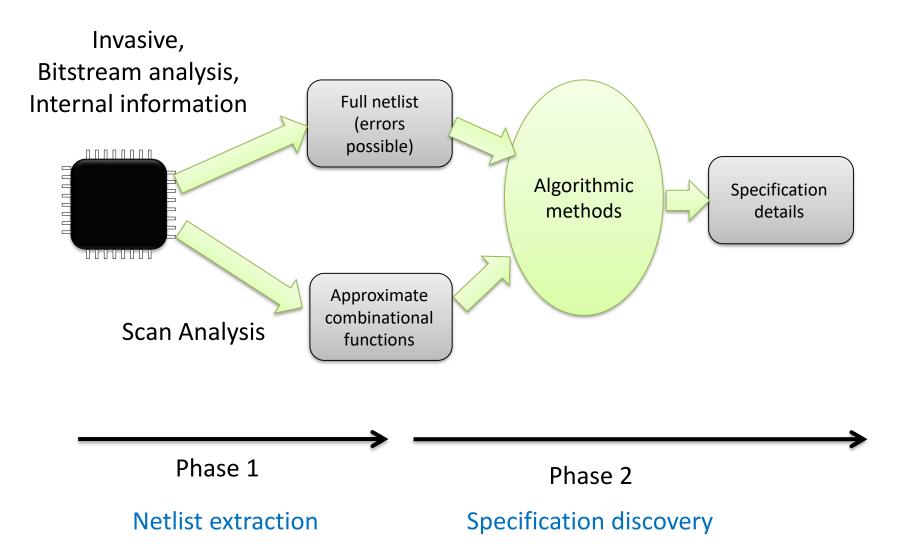

#### **Reverse Engineering of an IC**

Phase 1 IC -> Circuit

Phase 2 Circuit

Spec

- IC Reverse Engineering in a nutshell

- Scan-based netlist extraction

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Summary and Future Directions

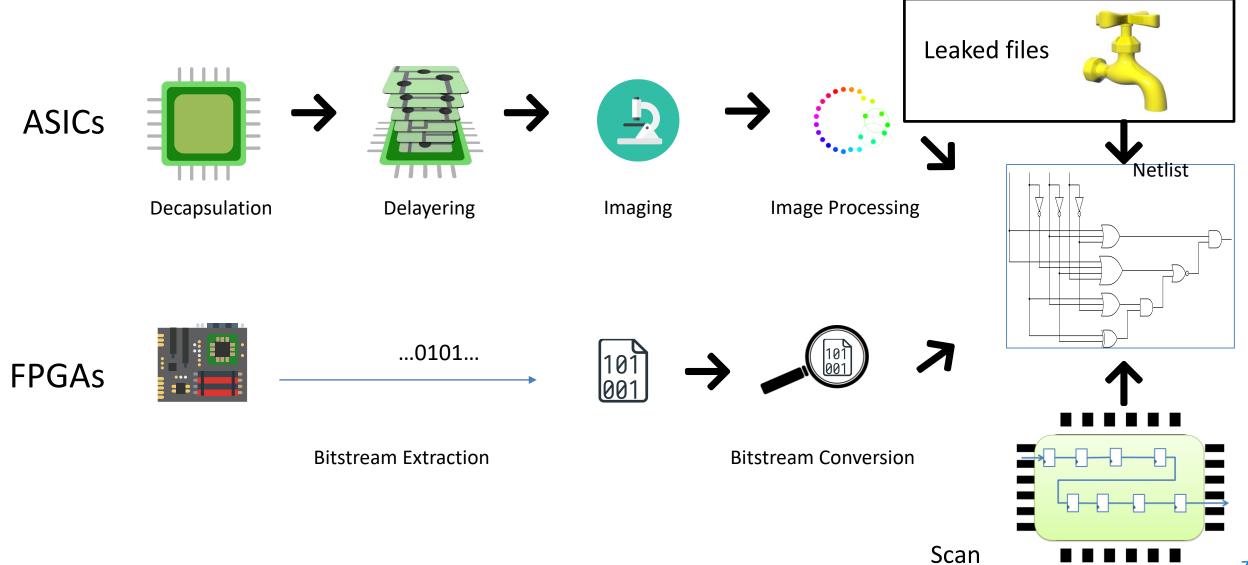

#### **Netlist Extraction**

Hiroshi Fujiwara Cyber Security Research Center

Ender et al, Insights into the Mind of a Trojan Designer. The Challenge to Integrate a Trojan into the Bitstream," ASP-DAC 2019

Production Tester

Azriel, "Revealing On-chip Proprietary Security Functions with Scan Side Channel Based Reverse Engineering," GLSVLSI 2017

Production Tester

Production Tester

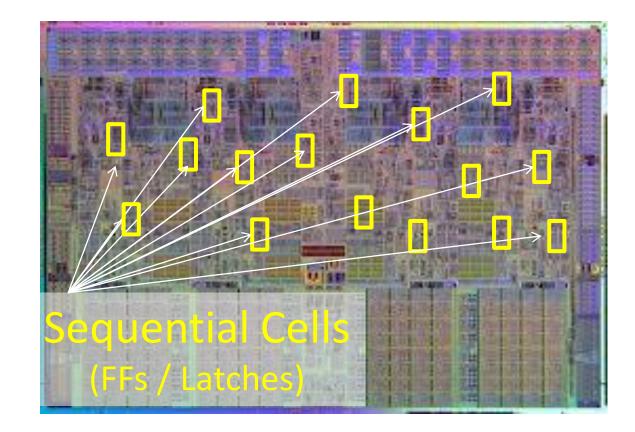

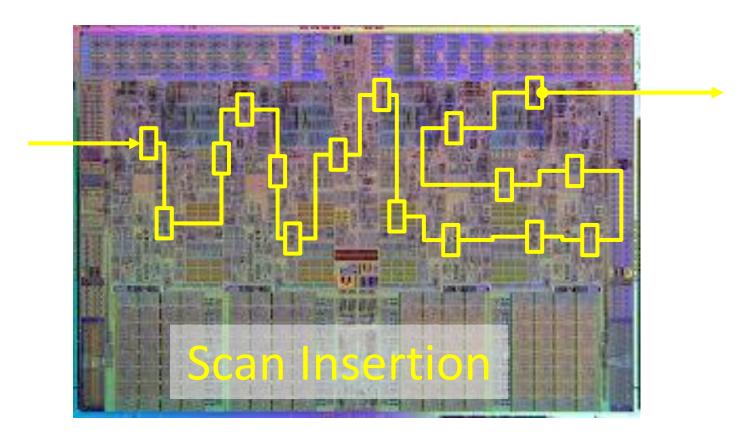

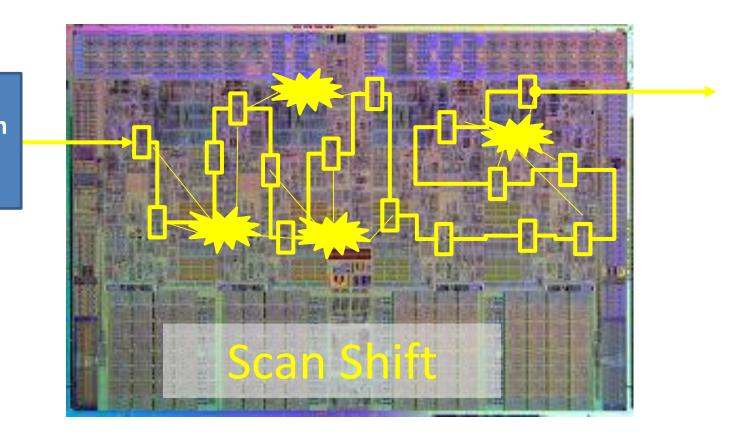

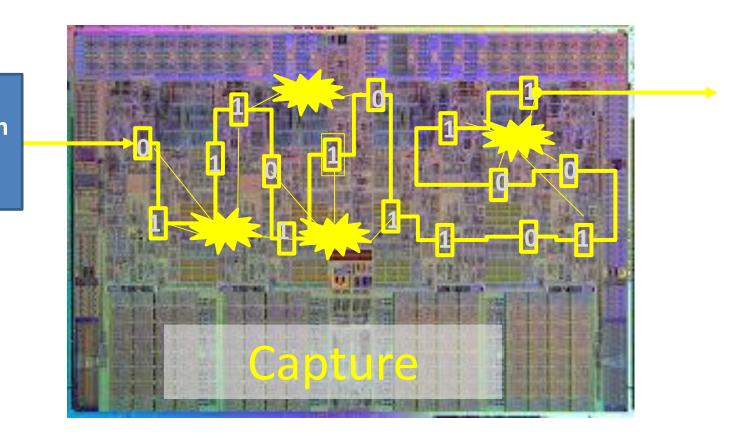

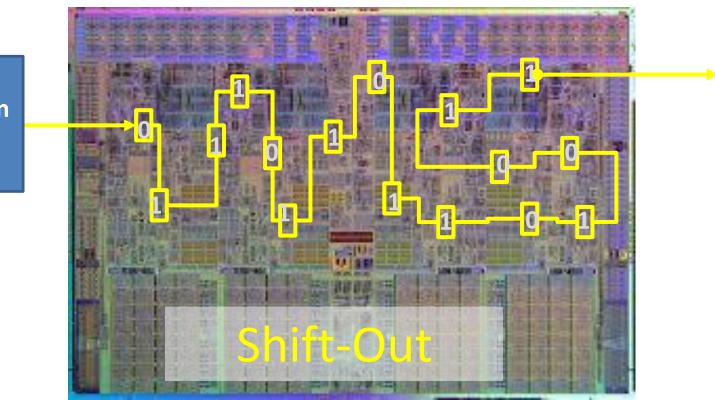

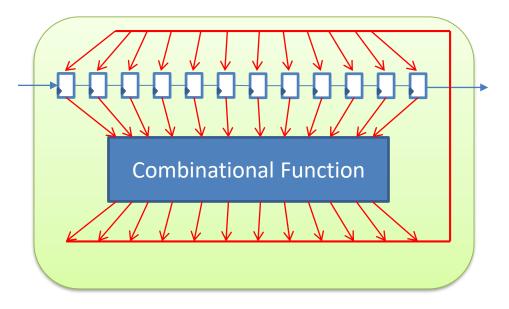

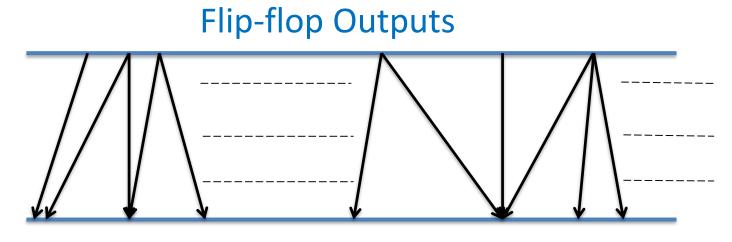

#### **Unfolding Sequential Circuits with Scan**

- Scan turns the IC to a stateless circuit

- Mapped to the Boolean Function Learning problem:  $\{0,1\}^n \rightarrow \{0,1\}^n$

#### **Unfolding Sequential Circuits with Scan**

- Scan turns the IC to a stateless circuit

- Mapped to the Boolean Function Learning problem:  $\{0,1\}^n \rightarrow \{0,1\}^n$

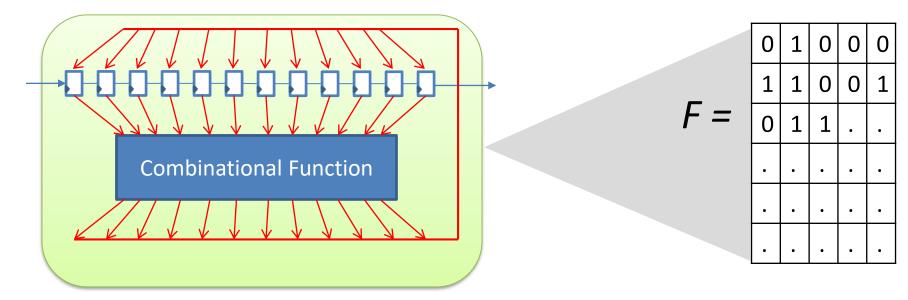

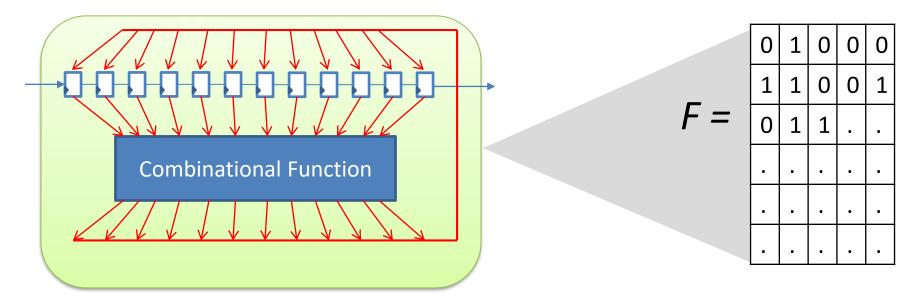

- Exhaustive Search: Extract the Truth Table by running queries for all inputs

- Scan turns the IC to a stateless circuit

- Mapped to the Boolean Function Learning problem:  $\{0,1\}^n \rightarrow \{0,1\}^n$

- Exhaustive Search: Extract the Truth Table by running queries for all inputs

- Exponential Size: 2<sup>n</sup>

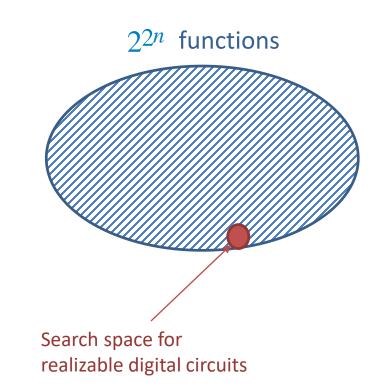

### Shannon Effect

Shannon Effect: "almost all" Boolean functions have a complexity close to the maximal possible (~O(2<sup>n</sup>)) for the uniform probability distribution

Corollary: For large n, "almost all" Boolean functions are not realizable in VLSI technology

In practice, logic cones have limited number of inputs:

<u>Transitive Fan In</u> = K

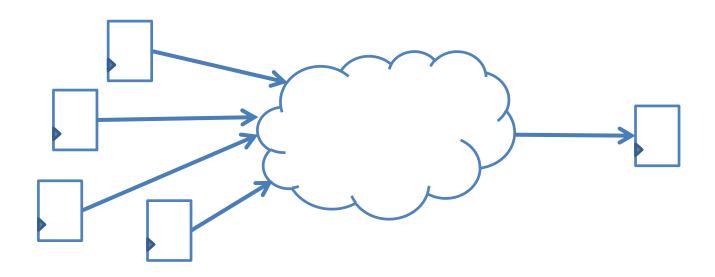

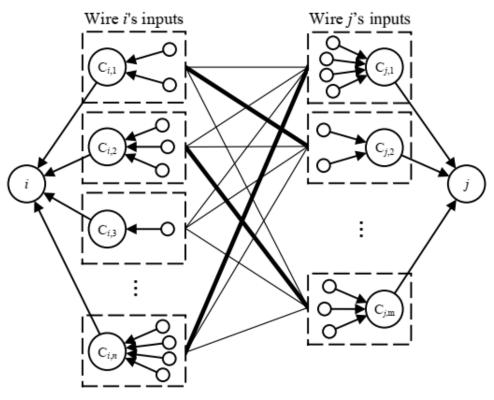

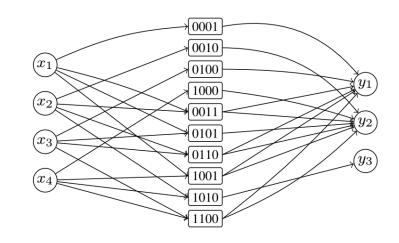

## Dependency Graph

Flip-flop Inputs

- Bipartite graph represents flip-flop dependencies

- The goal: Find dependencies

- Complexity:  $2^n \rightarrow 2^k$ : Scalable with the chip size

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

Generate random queries

$$y = f(\vec{x})$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$\vec{a} = \{0, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

Generate random queries

$$y = f(\vec{x})$$

$$\vec{b} = \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 1\}, f(\vec{b}) = 1$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$\vec{a} = \{0, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{b} = \{1, 0, \dots 1, 0, 1, 0, 0, \dots, 0, 1\}, f(\vec{b}) = 1$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$\vec{a} = \{0, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 1, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{b} = \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 1\}, f(\vec{b}) = 1$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$\vec{a} = \{0, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 1, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 1$$

$$\vec{b} = \{1, 0, \dots 1, 0, 1, 0, 0, \dots, 0, 1\}, f(\vec{b}) = 1$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$\vec{a} = \{0, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 1, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

н.

$$\vec{a} = \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 1$$

$$\vec{b} = \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 1\}, f(\vec{b}) = 1$$

$$y = f(\vec{x}), \vec{x} = \{x_1, x_2, \dots, x_i, x_{i+1}, \dots, x_j, \dots, x_n\}$$

$$\vec{a} = \{0, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 0, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

$$\vec{a} = \{1, 0, \dots, 1, 0, 0, 0, 0, \dots, 0, 0\}, f(\vec{a}) = 0$$

1 0 1 0 0

$$O\left(n \cdot \log n \cdot \mathbf{k} \cdot \mathbf{2}^k\right)$$

$$= \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 0\}, f(a) = 1$$

Relevant Variable

$$= \{1, 0, \dots, 1, 0, 1, 0, 0, \dots, 0, 1\}, f(\vec{b}) = 1$$

()

ā

$\vec{b}$

$(1 \cap$

Hiroshi Fujiwara

**Cyber Security**

**Research Center**

Assumptions

- Physical access to the device

- Scan operation protocol is known

- Vendors use proprietary protocols

- There are standard solutions by EDA vendors

- Scan control is not protected or protection is defeated

Or self-owned device

#### Assumptions

- Physical access to the device

- Scan operation protocol is known

- Vendors use proprietary protocols

- There are standard solutions by EDA vendors

- Scan control is not protected or protection is defeated

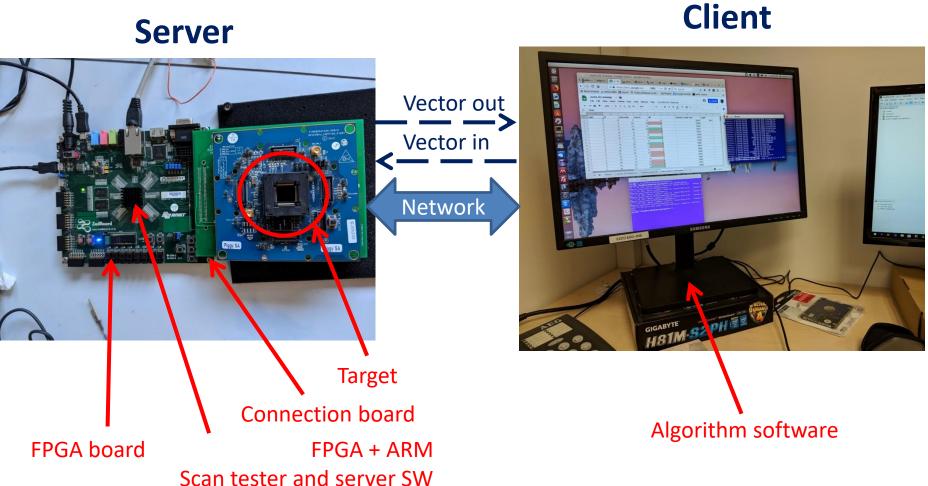

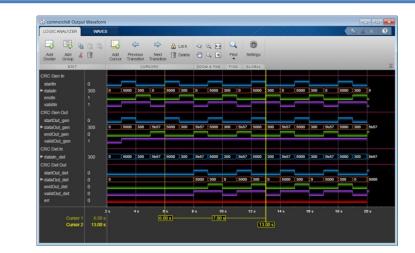

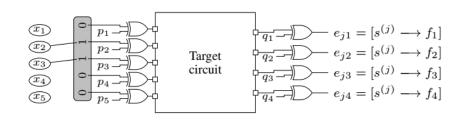

#### Scan-based netlist extraction setup

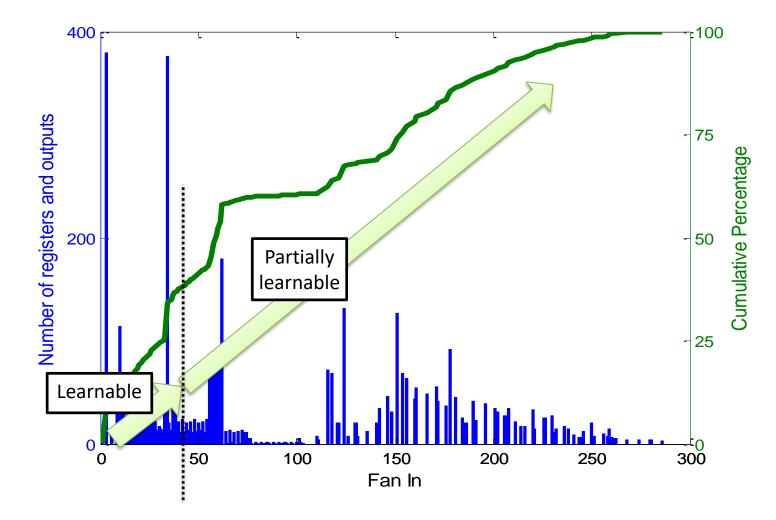

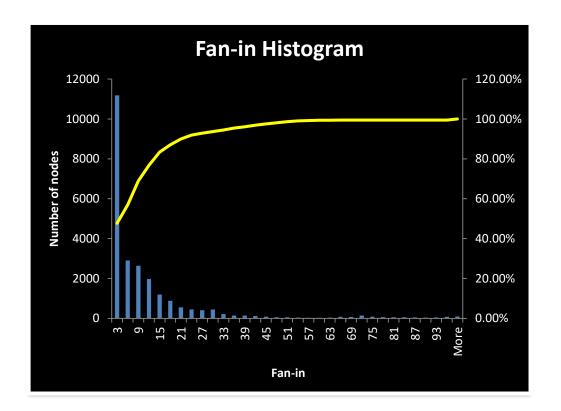

#### Fan-in analysis

- Partial data: not all dependencies discovered

- Estimation: vast majority is there

- Longer runs reveal few more links

~95% of logic cones can be directly reverse engineered at the logic function level

### The two phases

#### **Specification Discovery**

• What actually the spec is?

• No universal definition or format

- Can be

- Finding familiar elements

- Translating to a higher level language

- Goal dependent, e.g. finding specific properties

- IC Reverse Engineering in a nutshell

- Scan-based netlist extraction

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Summary and Future Directions

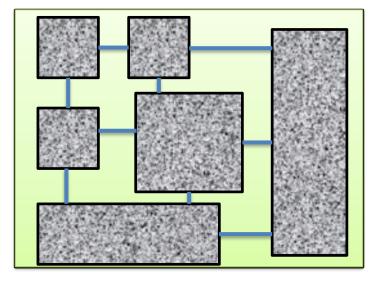

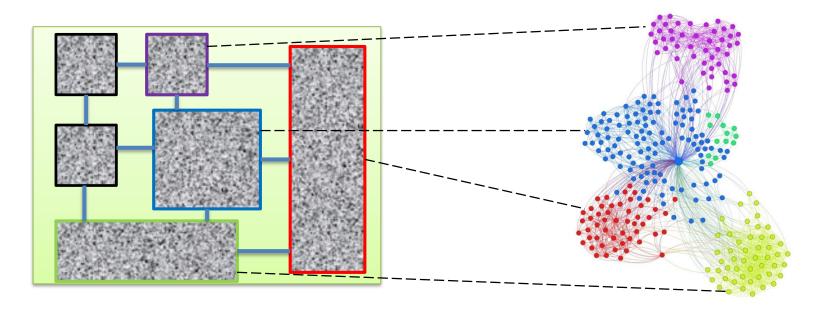

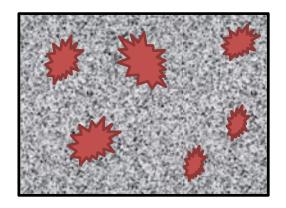

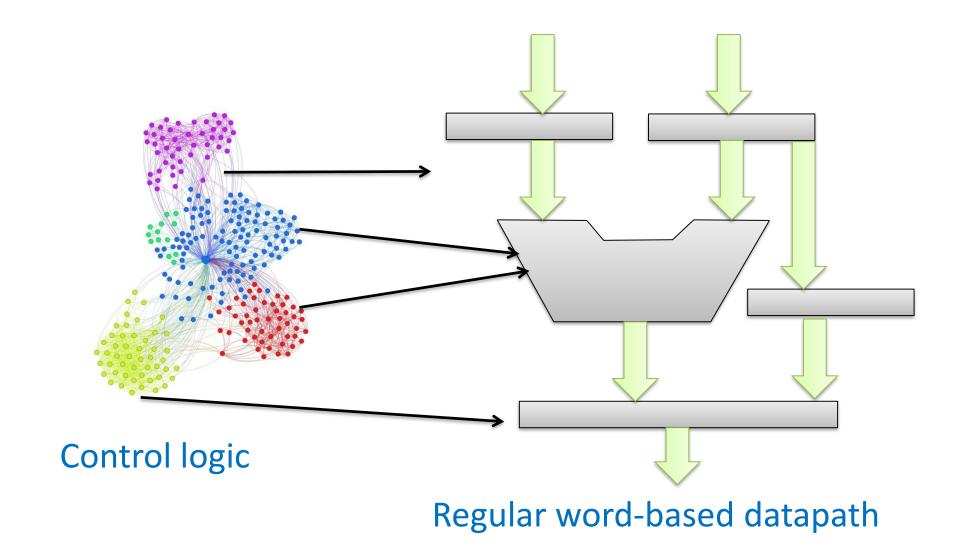

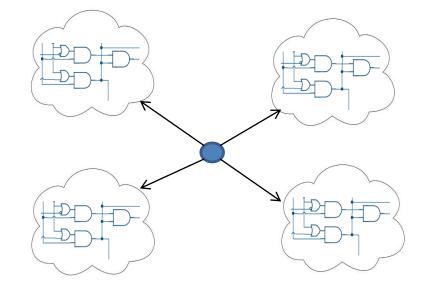

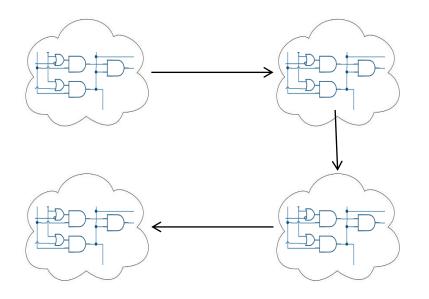

# **Circuit Partitioning**

• Find basic structure in the flat graph

## **Circuit Partitioning**

• Goal: match the source design partitioning

## **Circuit Partitioning**

- Goal: match the source design partitioning

- Criteria: wire density

## **Circuit Partitioning**

- Goal: match the source design partitioning

- Criteria: wire density

- Method: graph clustering

#### Minimum cut

- Partition a graph by removing minimum number of edges

- Widely used in the VLSI CAD tools

- Top-down approach

- Poor choice for our problem:

- Fixed number of partitions

- Uneven split

- Min-Ncut

- Normalized min-cut

$$NCut(A,B) = \frac{cut(A,B)}{assoc(A,V)} + \frac{cut(A,B)}{assoc(B,V))}.$$

- Modularity maximization

- Find best partition to maximize modularity

$$Modularity(G_i \in \mathbf{G}) = \frac{\left|E\right|_{G_i} - \left|E\right|_{G^*_i = \{V_{G_i}, E_{random}\}}}{\left|E\right|_G}$$

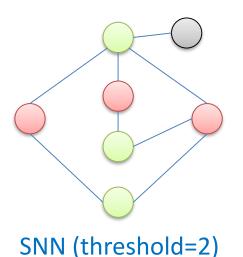

Every pair of nodes with <u>>threshold</u> shared neighbors are assigned to the same cluster

Bottom-up

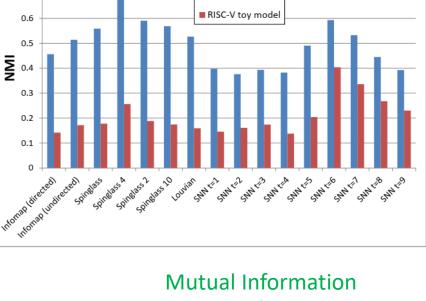

## **Clustering algorithms evaluation**

• Goal: match the original design hierarchy

Metric: Should reflect the goal

NMI: Normalized Mutual Information Information theoretical metric

UART

0.8 0.7

NMI =

- IC Reverse Engineering in a nutshell

- Scan-based netlist extraction

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Summary and Future Directions

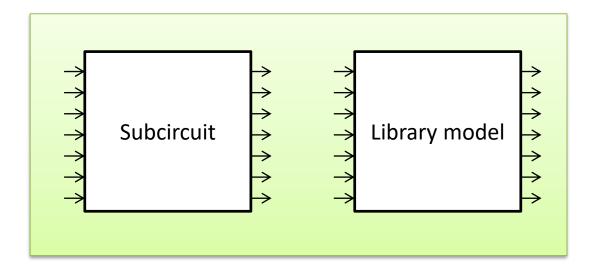

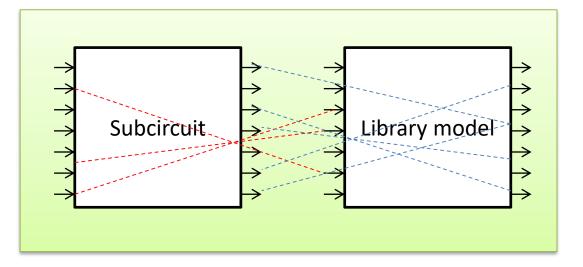

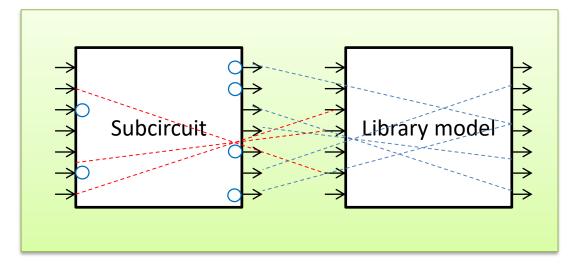

# Matching against a library

- Structural Analysis

- Syntactic match

- Isomorphism

- Less flexible

- Functional Analysis

- Semantic match

- Functional identity

- Static / simulations

Hiroshi Fujiwara

**Cyber Security**

**Research Center**

## Matching library components

- Subgraph isomorphism

- Structural match

- NP-complete

- Heuristics

- Dimension reduction

- Signatures

#### **NPNP-invariant matching**

#### **NPNP-invariant matching**

Input/output permutation

#### **NPNP-invariant matching**

- Input/output permutation

- Input/output negation

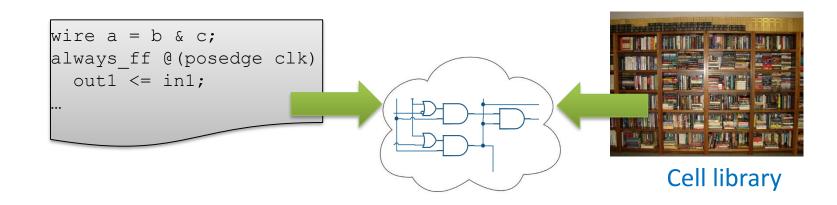

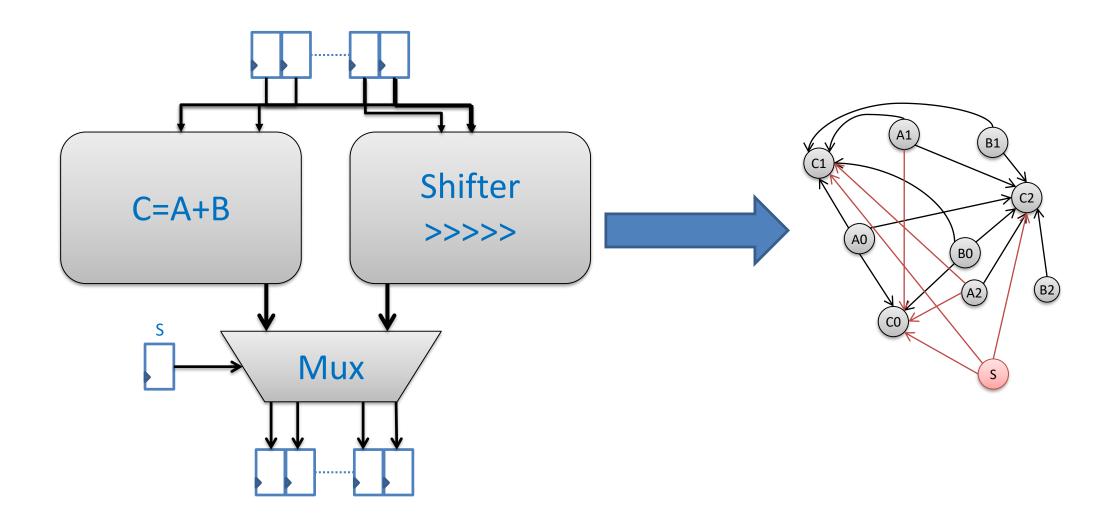

## **Technology mapping**

- RTL synthesis

- Map generic logic to technology cells

- npnp-invariant matching

## Outline

- IC Reverse Engineering in a nutshell

- Scan-based netlist extraction

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Summary and Future Directions

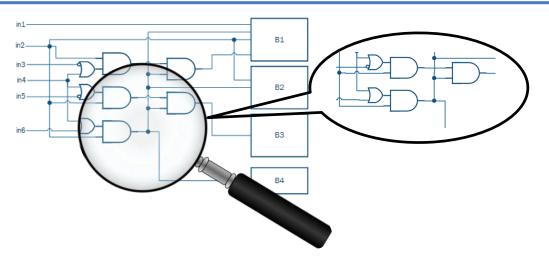

## Looking for more structure

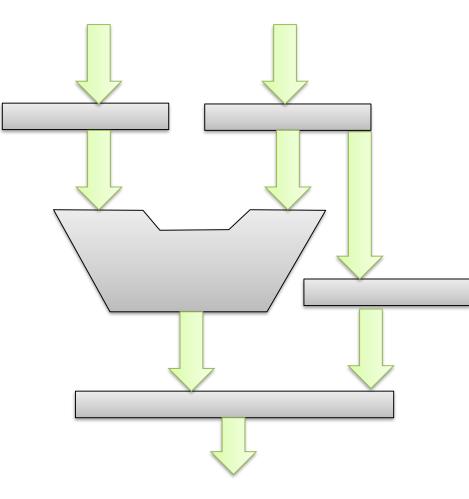

## WordRev: construct bit slices

6-Feasible cut (K-Feasible cut of N = K nodes that completely define the value of N)

## WordRev: group equivalent slices

#### Permutation-invariant Boolean matching

Li, "WordRev: Finding word-level structures in a sea of bit-level gates," HOST 2013

#### WordRev: group by connections

Parallel connection (e.g. MUX select)

Serial connection (e.g. carry propagation)

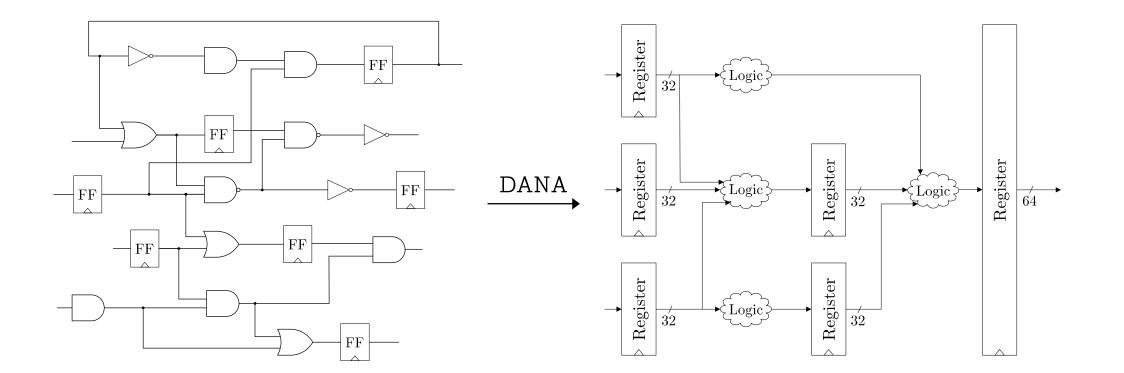

#### DANA - Universal Dataflow Analysis for Gate-Level Netlist Reverse Engineering

#### **RELIC tool**

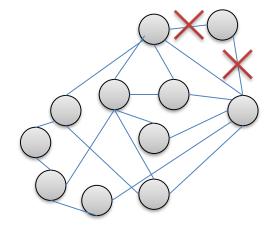

- Detecting registers in data words

- Loose topological comparison of fan-in structures

- Preprocess to simple gates

- Recursive search

- Similarity metrics

- Based on number of inputs

- Connecting nodes with similarity > threshold

- Mark registers with feedback path as FSM registers

- Too many false positives

- Mark registers with feedback path as FSM registers

- Too many false positives

- Narrowing down

- Select registers that control datapath

- Group registers that have the same enable signal

- Group registers that have shared gates in their combinational feedback path

## Outline

- IC Reverse Engineering in a nutshell

- Scan-based netlist extraction

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Summary and Future Directions

- Massively used in the VLSI design process

- Uses anchors

- Named registers

- Hierarchical boundaries

- Usually combinational match only

- Still a SAT problem, but there is a structure

• Some unsupervised learning used for clustering

• Can the full ML power be harnessed for RE?

• Problem: insufficient dataset

- Map a circuit to a library of 4-LUTs

- 222 isomorphism classes to make the LUT npn-invariant

- Existence vectors: classes of adjacent elements

- Reduced existence matrix is fed to CNN

- Total set of 250 synthetic circuits

- Efficient for a small number of classes

- One class (detect whether multiplier is present): 97% accuracy

- 9 classes: 75% accuracy

#### Spectral Graph Methods

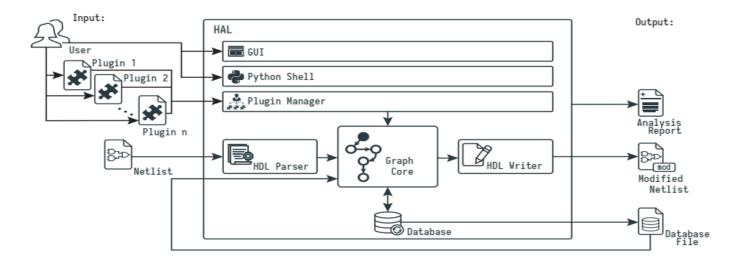

#### **Reverse Engineering Tools**

- Commercial

- ChipWorks

- Texplained ChipJuice (phase 1)

- Academia

- Degate (phase 1)

- -HAL

## Outline

- IC Reverse Engineering at a glimpse

- Partitioning

- The matching problem

- Structural Analysis

- Functional Analysis

- Algorithmic Reverse Engineering Tools

- Summary and Future Directions

- Uniform output format

- Streamline the research

- Evaluation baseline and common metrics

- Quantifying success

- How to measure spec information

- Is number of classified gates the right metric

- Graph methods

- Take advantage of the big advancement in the social network analysis

- Functional analysis

- Use Boolean function properties

- Machine learning

- Generate a synthetic data set

- Generative Adversarial Networks

- One-shot learning

- Protection

- Logical obfuscation

- Structural obfuscation

# Questions

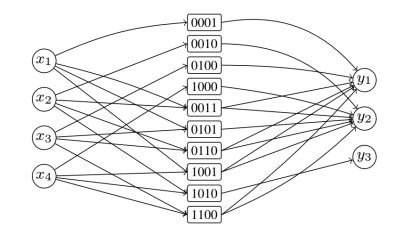

## Matching using simulation vectors

- Permutation invariance

- One-hot and two-hot vectors

- Simulation graphs

- Matching subgraphs

## Matching using simulation vectors

- One-hot and two-hot vectors

- Simulation graphs

- Matching subgraphs

- Negation invariance

- Add polarity variables

- SAT problem

Hiroshi Fujiwara

Research Center

**Cyber Security**