Haojie Ye University of Michigan Ann Arbor, Michigan, USA yehaojie@umich.edu

Yichen Yang University of Michigan Ann Arbor, Michigan, USA yangych@umich.edu Sanketh Vedula Technion Haifa, Israel sanketh@campus.technion.ac.il

> Alex Bronstein Technion Haifa, Israel bron@cs.technion.ac.il

Trevor Mudge University of Michigan Ann Arbor, Michigan, USA tnm@umich.edu Yuhan Chen University of Michigan Ann Arbor, Michigan, USA chenyh@umich.edu

Ronald Dreslinski University of Michigan Ann Arbor, Michigan, USA rdreslin@umich.edu

Nishil Talati University of Michigan Ann Arbor, Michigan, USA talatin@umich.edu

## ABSTRACT

The high memory bandwidth demand of sparse embedding layers continues to be a critical challenge in scaling the performance of recommendation models. While prior works have exploited heterogeneous memory system designs and partial embedding sum memoization techniques, they offer limited benefits. This is because prior designs either target a very small subset of embeddings to simplify their analysis or incur a high processing cost to account for all embeddings, which does not scale with the large sizes of modern embedding tables. This paper proposes GRACE-a lightweight and scalable graph-based algorithm-system co-design framework to significantly improve the embedding layer performance of recommendation models. GRACE proposes a novel Item Co-occurrence Graph (ICG) that scalably records item co-occurrences. GRACE then presents a new system-aware ICG clustering algorithm to find frequently accessed item combinations of arbitrary lengths to compute and memoize their partial sums. High-frequency partial sums are stored in a software-managed cache space to reduce memory traffic and improve the throughput of computing sparse features. We further present a cache data layout and low-cost address computation logic to efficiently lookup item embeddings and their partial sums. Our evaluation shows that GRACE significantly outperforms the state-of-the-art techniques SPACE and MERCI by  $1.5 \times$  and  $1.4 \times$ , respectively.

## **CCS CONCEPTS**

• Computer systems organization → Cloud computing.

ASPLOS '23, March 25-29, 2023, Vancouver, BC, Canada

© 2023 Copyright held by the owner/author(s). Publication rights licensed to ACM. ACM ISBN 978-1-4503-9918-0/23/03...\$15.00 https://doi.org/10.1145/3582016.3582029

#### **KEYWORDS**

DLRM, Embedding Reduction, Algorithm-System Co-Design

#### **ACM Reference Format:**

Haojie Ye, Sanketh Vedula, Yuhan Chen, Yichen Yang, Alex Bronstein, Ronald Dreslinski, Trevor Mudge, and Nishil Talati. 2023. GRACE: A Scalable Graph-Based Approach to Accelerating Recommendation Model Inference. In Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3 (ASP-LOS '23), March 25–29, 2023, Vancouver, BC, Canada. ACM, New York, NY, USA, 20 pages. https://doi.org/10.1145/3582016.3582029

## **1** INTRODUCTION

Deep Learning Recommendation Models (DLRMs) are widely employed to predict rankings of news feeds and entertainment content [18, 21]. An earlier work [26] shows that DLRMs consume a majority of AI inference cycles of data centers. DLRM exhibits a mix of workload characteristics with fully connected *dense* neural network layers and *sparse* embedding layers. The sparse embedding layers are the primary performance bottlenecks of DLRM execution due to their high memory bandwidth requirement [24, 26, 28, 34, 38, 43, 44]. Because this application runs at a population scale, the execution bottlenecks significantly increase the Total Cost of Ownership (TCO) and power consumption of data centers [5, 35]. Therefore, improving DLRM performance directly results in saving millions of dollars in cost and carbon emission [66].

The key challenge in accelerating the DLRM embedding layer performance is to exploit spatial and temporal locality. This challenge is because of the irregular nature of the workload's memory access pattern over large embedding tables. Recently, several techniques have attempted to improve the DLRM embedding layer inference performance either by caching partial sums of embeddings leading to reduced memory traffic [34, 48] or by exploiting the heterogeneous memory systems [1, 34, 38]. These approaches, however, fall short in the following manner. First, FAE [1] and Rec-NMP [38] employ heterogeneous memory systems to exploit the power-law in the item access frequency distribution; however, they do not improve the memory traffic. Second, SPACE [34] employs

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

a heuristic threshold to select a small subset of popular items and stores exhaustive combinations of two-item partial sums that leads to low memory bandwidth reduction. Third, MERCI [48] employs an expensive user trace processing technique to store partial sums of more than two items. It has three main drawbacks: (i) the algorithm does not scale to large embedding tables, (ii) the algorithm operates on the level of sub-groups of embeddings and it does not capture a global view of user-item interactions; thus the resulting partial sum formation is based on a limited scope of user-item interactions, leading to sub-optimal memory traffic reduction, and (iii) its design is unaware of memory heterogeneity. An ideal design goal is to significantly *reduce memory traffic* while *exploiting memory heterogeneity* in a *scalable* fashion.

This paper presents GRACE—a scalable graph-based algorithmsystem co-design that significantly improves the memory system performance of DLRM embedding reduction on commodity hardware. Due to the software-only nature of its design, GRACE can be immediately deployable in today's data centers. The design goals of GRACE are four-fold: (1) exploit spatial and temporal locality in the workload, (2) significant memory traffic reduction, (3) memory heterogeneity awareness, and (4) scalability to large embedding table sizes. To this end, we cast the problem of scalably identifying popular item combinations of arbitrary lengths to a graph problem. Using the outcome of this problem, we present a generic system design framework to improve DLRM performance.

Specifically, GRACE analyzes the item preferences of different users to construct an Item Co-occurrence Graph (ICG). Nodes in this graph represent items, and edge weights represent the number of times two items are co-accessed. Mapping co-occurrence frequencies to a graph offers a global view of co-occurrence events that can scale to a large number of users/items. We then propose a novel clustering algorithm for ICG that finds frequently accessed item combinations. Each resulting cluster is a set of co-accessed items. To best exploit this algorithmic framework, GRACE stores the partial sums of frequently co-accessed item combinations into a software-managed cache space. The ICG clustering algorithm is cache layout aware. GRACE effectively navigates the trade-off between memory traffic reduction and heterogeneous memory bandwidth utilization by appropriately distributing partial sums and single-item embeddings into cached and non-cached spaces. ICG construction and clustering, and partial sum cache data injection are performed offline without affecting ongoing inference cycles. At runtime, GRACE exploits both cached partial sums and frequently accessed single-item embeddings to significantly reduce the memory traffic and improve spatial and temporal locality.

To showcase the effectiveness of GRACE, we use a case study of a heterogeneous CPU-GPU system, widely deployed in today's data centers [25, 45, 63, 76] for executing DLRMs. In this system, the capacity-limited GPU memory acts as a software-managed cache. Our evaluation<sup>1</sup> shows that GRACE outperforms the stateof-the-art techniques SPACE [34] and MERCI [48] by 1.5× and 1.4×, respectively. We further show that GRACE reduces the memory traffic of embedding reduction by 1.5× and 1.1× over SPACE and MERCI. GRACE also improves performance over prior works by balancing the traffic between the heterogeneous memory system. The graph clustering algorithm in GRACE scales well with the increase in the number of user/items, reducing the processing cost by 8.3× compared to MERCI. The scalable nature of GRACE enables analysis of large user-item interaction traces and embedding tables in a practical fashion. We demonstrate the generality of GRACE by presenting case studies of two additional hardware platforms: 1) a homogeneous GPU memory and 2) a DIMM-HBM heterogeneous memory with Processing-In-Memory (PIM) capability. These studies show consistent improvements of GRACE over prior systems.

Compared to the state-of-the-art system MERCI, GRACE makes the following novel contributions. First, GRACE fundamentally redesigns the problem of finding frequently accessed item combinations by formulating it as a graph problem. This formulation provides a global view of the user-item access trace, as opposed to MERCI, which operates with a limited scope of user-item interactions. Second, GRACE proposes a scalable clustering algorithm whose complexity grows linearly with the number of items and is independent of the number of users. To compare, the runtime complexity of MERCI is quadratic in the number of items and increases linearly with the number of users. Third, GRACE design is memory heterogeneity-aware, which caters to the data center system modeling of the DLRM workload deployment [24, 63], while MERCI is designed only for homogeneous memory systems.

To summarize, the key contributions of GRACE are as follows:

- Casting the problem of finding popular item combinations in DLRM to a graph problem.

- Introduction of novel Item Co-occurrence Graph (ICG) that scalably records co-accessed item combinations for DLRM.

- A system-aware and scalable graph clustering algorithm aimed at finding arbitrary-length popular item combinations within the capacity-limited cache space.

- GRACE—an algorithm-system co-design that reduces memory traffic and exploits heterogeneous memory system to improve end-to-end DLRM throughput by 1.40× and 1.35× compared to the state-of-the-art frameworks SPACE [34] and MERCI [48], respectively.

- GRACE is open-source for the benefit of the broader research community: https://github.com/Linestro/GRACE.

#### 2 BACKGROUND

#### 2.1 Personalized Recommendation Models

The goal of DLRM is to predict the Click-Through Rate (CTR) [13, 18, 54, 72, 78], *i.e.*, the probability of a user clicking on an advertised item. A major data center operator Meta (previously Facebook) has claimed [26] that DLRM models consume more than 60% of their AI inference cycles in production, which makes them a leading candidate for optimization. In contrast to traditional deep neural network (DNN) models, DLRM features a hybrid architecture of multi-layer perceptron (MLP) models and embedding layers. The "dense" input features (*e.g.*, age, gender, and location of the user) are processed by the first MLP to generate dense features. The sparse input features (*e.g.*, previous user-item interactions), on the other hand, are processed by the embedding layers. An embedding layer contains a large embedding table that stores feature vectors of different items. A user's past interactions with items are used

<sup>&</sup>lt;sup>1</sup>We use an in-house implementation for SPACE [34], and open-source implementation [3] of MERCI [48] by the authors.

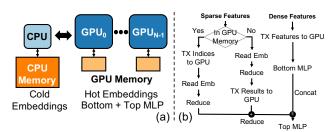

Figure 1: (a) A heterogeneous CPU-GPU system executing DLRM inference, and (b) workflow of DLRM inference execution with a heterogeneous system.

to index these tables to extract items' features. These features are then reduced to represent the summary of the user's interests. This layer performs sparse computation because a user only interacts with a handful of items out of millions of available items. These sparse and dense features are thereafter concatenated and fed into another MLP layer to predict the CTR.

#### 2.2 DLRM Inference with GPU Support

DLRM systems in production [25, 45, 63, 76] employ a hybrid CPU-GPU design to execute MLPs and memory-bandwidth-demanding embedding layers in DLRM models. A simplified depiction of executing DLRM models on a hybrid CPU-GPU system is presented in Fig. 1(a). GPU executes MLPs to exploit higher compute throughput. The high-bandwidth GPU memory is used to handle the memory bandwidth-intensive reduction operations of the embedding layers. However, the embedding tables that store all item features can amount from tens of GBs to TBs, making it impossible to fit the entire table into GPU memory. Thus, the GPU memory acts as a software-managed cache space to store a portion of the embedding tables [1, 25, 34, 45, 63]. Low-bandwidth CPU memory with high capacity is employed to store and reduce the rest of the embedding entries that do not fit in the GPU. We further show in Fig. 1(b) the state-of-the-art DLRM inference framework that incorporates a GPU. After receiving a batch of user requests, the requested embedding indices are transferred (TX) to the GPU and are evaluated for whether each of them is on CPU or GPU. The embedding reduction operations will distribute to the corresponding memory and CPU/GPU reduces the embeddings to produce the results for each user before the results are finalized on GPU for top MLP layers.

#### 2.3 Exploiting Popular Choices in DLRMs

Real-world DLRM inputs follow a power-law distribution [1, 22, 48, 58, 68], where a small collection of popular items accounts for a large fraction of embedding table accesses. Below, we summarize prior works that exploit power-law distribution for optimization.

- *FAE* [1] proposes a framework that constructs an empirical distribution of item access frequencies by profiling a portion of the user-item access trace. The framework then calibrates a popularity threshold and uses the GPU memory to store the highly accessed embeddings.

- *RecNMP* [38] proposes a small cache structure to each ranklevel near-memory processing module to bypass the DRAM loads of frequently accessed items.

- *SPACE* [34] employs a hybrid memory architecture with HBM and DIMM, where HBM stores popular user choices. SPACE introduces two new concepts called *gather locality*

- and *reduction locality*. The power-law nature of the item access frequencies implies that preferential treatment of popular items (*i.e.*, placing them in HBM) can promote gather locality. Reduction locality, on the other hand, is availed by storing partial reductions of *any* two popular item vectors. Specifically, SPACE uses psum2, *i.e.*, reduction of embedding vectors of pairs of popular items. To exploit these two types of locality, SPACE pre-processes the user-item access trace to extract popular item choices and their combinations. These popular embedding vectors are stored in capacity-limited HBM that enables high-bandwidth access, while other embedding vectors are extracted from DIMMs.

- MERCI [48] generalizes SPACE by storing partial sums of more than two items. MERCI inspects the user-item interaction trace, analyzes popular co-accessed items, and merges them into clusters. Within the cluster, all partial sums are stored using the additional DRAM storage.

## 3 UNDERSTANDING THE CHALLENGES IN ACCELERATING DLRM INFERENCE

#### 3.1 Growing Data Sizes and Demands

The recent development of DLRM observes a super-linear growth of capacity and bandwidth demands. The evolution in DLRM has resulted in much richer embedding features, leading to increased data volumes. The memory footprint of DLRM has increased by 16 times, reaching an order of terabytes within four years [52, 77]. Additionally, the inherently irregular nature of memory accesses over large embedding tables results in a significant portion of accesses that cannot be served using capacity-limited caches, increasing the off-chip memory bandwidth requirements. The bandwidth demand of DLRM embedding layers has increased by 30 times to 2TB/s, dramatically outpacing the bandwidth growth of accelerator memories and interconnections [63].

#### 3.2 Limitations of Prior Works

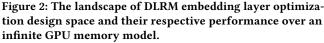

Fig. 2(a) shows the landscape of optimization directions divided into memory traffic reduction and heterogeneous memory aware placement for better memory bandwidth utilization. The goal is to achieve both high memory traffic reduction and high memory bandwidth utilization of the heterogeneous memory at the same time. However, we show in the following that none of the prior works supports designs in both optimization directions, and thus, results in sub-optimal performance.

**Memory traffic reduction.** In what follows, we discuss prior works that attempt to improve the DLRM embedding layer performance. As many items are frequently accessed together, these works propose storing their partial sums, resulting in a memory traffic reduction. **SPACE** [34] uses a subset of the most popular

H. Ye, S. Vedula, Y. Chen, Y. Yang, A. Bronstein, R. Dreslinski, T. Mudge, and N. Talati

items and caches partial sums (*psum*) all two–item combinations of popular items to produce *reduction locality*. This reduces the memory bandwidth requirement. However, we show that SPACE only reduces the memory traffic by 1.09× on average (detailed in Fig. 10). While the most popular single items are likely to be accessed by different users, there is no guarantee of users accessing *all possible* two popular item combinations frequently. We find that only an average of 25% of popular *psum* of two items stored in SPACE represent 95% of the accesses to the cache space. This shows that a majority of cached partial sums in SPACE are accessed significantly less frequently. This caching space can be better utilized by storing other more frequent patterns. Also, SPACE only tracks *psums* among  $O(\sqrt{n})$  frequently accessed items, where *n* is the number of items, making the strategy unscalable to large datasets.

MERCI [48] finds that items that co-occur can benefit from memoization of their partial sums. Such memoization can be generalized to clustering the co-occurred items and storing all psums within each cluster. MERCI proposes generating the most cost-efficient item clusters to fill the cache space. However, the main drawback is the complexity of generating such clusters. MERCI first classifies each item as a single-item cluster and recursively measures the benefit of merging any two clusters. By merging two clusters, all the partial sums within the clustered items are stored to reduce the memory bandwidth requirement. The amount of bandwidth reduction is measured by inspecting the inverse map of the *full* training trace. The clustering incurs an overhead of  $O(C \times n^2 \times m)$ , where *C* is the maximum capacity of generating *psums*, *n* is the number of items and *m* is the number of users in the training trace. In practice, MERCI breaks the total item set into k sub-groups using an off-theshelf algorithm [8] and only merges within the sub-group. This reduces the complexity to  $O\left(C \times k \times \left(\frac{n}{k}\right)^2 \times m\right)$ . Nevertheless, the complexity of MERCI grows super-linearly with the increase in the number of items and number of users, making the algorithm not scalable to large datasets.

**Memory heterogeneity awareness.** Both **FAE** [1] and **Rec-NMP** [38] set a heuristic threshold to distribute popular items to GPU/RankCache and exploit the high bandwidth memory of the heterogeneous system. **SPACE** stores popular embeddings (and *psums*) to produce gather locality.

To analyze the importance of memory heterogeneity awareness, we measure the performance of executing DLRM on a host machine that uses a heterogeneous memory system (configuration detailed in §6). For baseline performance analysis, we assume an infinite GPU memory capacity and naively migrate all embeddings (no psums) to the cache space, i.e., the GPU memory. We further tested an oracleof-2 framework that assumes psum of any 2 item embeddings can be accessed, and memory throughput on the heterogeneous memory system achieves a perfect balance between the CPU and GPU memory. While an oracle-of-3 or more is possible, we choose an oracle-of-2 to compare with MERCI and GRACE because it provides a reasonable roofline for the reduction factor. Fig. 2(b) shows that with the same additional capacity on GPU, two strategic frameworks SPACE and MERCI only outperform the baseline by  $1.14 \times$  and  $1.20 \times$  on average, while oracle-of-2 outperforms the baseline by 2.16×. We conclude 2 key reasons for this gap.

(a) Low memory traffic reduction ratio. The main speedup of SPACE stems from setting a heuristic threshold and storing popular item embeddings on HBM. This empirically distributes the traffic to both CPU memory and GPU memory, achieving a higher collective bandwidth. However, the traffic reduction ratio only goes up to 1.09× in SPACE due to the reduction strategy being unscalable to large datasets. FAE and RecNMP fall into the same category with a traffic reduction ratio of 1 (no reduction).

(b) Lack of heterogeneous memory awareness. MERCI finds items clustering assignments that maximize the memory traffic reduction using *psums*. However, this does not necessarily lead to optimal performance. By caching *psums* to the capacity-limited GPU, the bandwidth requirement is reduced, but this comes at the cost of excessively populating the cache space with *psums* that are rarely accessed. The occupied memory capacity for storing such *psums* prevents adding single-item embeddings to the GPU. This causes many item embeddings to be accessed from DIMM-based low bandwidth memory, throttling the overall memory throughput (detailed in §7.1). An ideal clustering algorithm should be memory *heterogeneity aware and balance the trade-off between memory traffic reduction and the heterogeneous memory throughput to achieve optimal performance.*

## 3.3 Challenges in Scalable System Design

Today's DLRM models involve several million items accessed by tens of millions of users [52, 77]. Scalably identifying frequently accessed item combinations that result in an effective memory traffic reduction remains a major challenge. Additionally, prior works do not systematically optimize for a *collective* bandwidth reduction of the heterogeneous memory system, resulting in a memory throughput imbalance.

#### **4 GRACE ALGORITHMIC FRAMEWORK**

This section presents a novel algorithmic framework of GRACE to tackle the aforementioned challenges. The framework designs the content of the capacity-limited cache space to maximize the DLRM inference performance. The designed cache space can contain both popular item embeddings and partial sums of item combinations of arbitrary lengths. We then present complexity and runtime overhead analysis to demonstrate the practicality of our algorithm.

#### 4.1 Design Goals

The goal of the GRACE algorithmic framework is to make the most efficient use of the cache space to store frequently accessed items and their combinations, given the capacity limitation. In particular, the algorithmic framework must meet the following expectations:

- *No exhaustive caching*. As discussed in §3, storing all pairs of highly accessed items leads to an  $O(n^2)$  space complexity, where *n* is the number of highly accessed cached items. In this setting, it is not guaranteed for all of the two frequently accessed items to be frequently *co-accessed*; caching partial sums of rarely co-accessed items wastes cache space. Thus, the algorithm must *not* exhaustively cache all the possible partial sums of highly accessed items.

- *Scalable with trace size.* The algorithm to build the cache space must have low complexity. In practice, the user-item interaction trace size can grow infinitely, and the number of users and items can scale to many millions. Therefore, a

high-complexity algorithm to find popular partial sums to cache can lead to prohibitive analysis times.

System awareness. The algorithm should account for different dataset characteristics and underlying system configurations, and be extensible to multiple embedding tables to achieve optimal performance in realistic deployment environments.

## 4.2 Algorithm Details

Given the user-item interaction trace, the goal of the algorithm is to find the most frequently accessed items and item combinations. Naively counting frequencies of all item combinations results in a combinatorial explosion, thus it is not feasible even for a small number of item combinations. To tackle this problem, here we introduce the notion of an Item Co-occurrence Graph (ICG). In an ICG, the nodes represent items, and edge weights represent the frequency of co-occurrence of items across the sampled user access patterns. We cast the problem of scalably tracking frequencies of arbitrary-sized item combinations as a graph problem on the ICG. The user-item interaction trace can have different orders of items being accessed (i.e., irregular accesses) by users, and the trace size can grow infinitely. Key advantages of representing useritem interaction trace via ICG are (i) the graph size is invariant to the number of users, (ii) it is an order-agnostic representation of user-item trace, (iii) the number of nodes in the graph grows only linearly in the number of items. Heavily weighted edges in the ICG efficiently capture highly co-accessed combinations of items gathered from all user-item interactions. Thus, ICG provides a succinct global view over the user-item interaction trace, and allows for the design of efficient graph analysis algorithms that scale to large numbers of users and items. In what follows, we present a unified algorithmic framework that identifies frequently accessed single items and their combinations using the ICG. This is a two-phase algorithm: the first phase records user preferences and constructs of the ICG, and the second phase clusters this graph to find popular items and their combinations.

ICG Construction Phase. We are provided with sampled historical data of items accessed by users. Each user has a list of accessed items organized in a data structure user\_accesses. We use these user-item accesses to construct the ICG which contains the frequency of co-occurrence of items aggregated across users. Alg. 4 (see Appendix §A.1) presents the pseudo-code of this graph construction phase. To build the ICG, we first randomly sample users. For each sampled user, we buffer all pairs of items accessed by the user as item co-occurrences. We then use this item cooccurrence buffer to construct a weighted graph by increasing the edge-weight by 1 for each co-occurrence. The buffer of edges/item co-occurrences can be constructed online by a fire-and-forget process without impacting the performance of ongoing DLRM inference; the weighted ICG is constructed offline during the cache design phase. Further discussion on our proposed usage model is presented in the sequel (§5.1).

**ICG Clustering Phase.** This phase clusters the ICG. The goal of this algorithm is to identify frequently occurring item combinations from the user access patterns. Post clustering, the nodes (items) from the same cluster are deemed to be accessed together frequently. One way to cluster the graphs is by employing off-the-shelf graph clustering algorithms such as Metis [46]. Notably, these clustering

| o clusters |

|------------|

|            |

| -   |                                                                                                |

|-----|------------------------------------------------------------------------------------------------|

|     | rocedure ClusterICG() > Offline ICG clustering                                                 |

| 2:  | Input: G: Item Co-occurrence Graph (ICG)                                                       |

| 3:  | Input: nodes: Vertex set of G sorted by their degrees                                          |

| 4:  | Input: capacity_budget: Number of cache lines allowed in cache space                           |

| 5:  | Output: cluster_list: Assignment of ICG nodes into different clusters                          |

| 6:  |                                                                                                |

| 7:  | <pre>node_idx=0; cluster_id=0; occupied_space= nodes </pre>                                    |

| 8:  | active_list[u]=0, $\forall u \in nodes$ $\triangleright$ indicator whether a node is clustered |

| 9:  | while node_idx <  nodes  do                                                                    |

| 10: | anchor_node = nodes[node_idx]                                                                  |

| 11: | remaining_memory = capacity_budget - occupied_space                                            |

| 12: | // Create a cluster using an anchor node                                                       |

| 13: | cluster = FormCluster(G, anchor_node, active_list,                                             |

| 14: | remaining_memory)                                                                              |

| 15: | // Calculate occupied space, break if OOM                                                      |

| 16: | occupied_space += 2 <sup>cluster.size()</sup> - 1 - cluster.size()                             |

| 17: | <pre>if occupied_space &gt;= capacity_budget then</pre>                                        |

| 18: | break                                                                                          |

| 19: | cluster_list[cluster_id] = cluster                                                             |

| 20: | cluster_id += 1                                                                                |

| 21: | <pre>while !active_list[nodes[node_idx]] do</pre>                                              |

| 22: | node_idx += 1   increment until reaching the first active node                                 |

| 23: | return cluster_list                                                                            |

algorithms optimize for different criteria and do not create clusters that minimize DLRM bandwidth as we show in §7.

GRACE proposes a novel clustering algorithm that *clusters the* graph with the objective of maximizing bandwidth reduction in DLRM. Our proposed algorithm is *caching space-aware*, *i.e.*, it also accounts for capacity-limited cache space for clustering decisions. Post clustering, GRACE caches the partial sums of embeddings of all item combinations within each cluster. During inference, these cached partial sums are used to (i) reduce memory traffic, and (ii) avail efficient memory accesses to increase end-to-end DLRM throughput.

Alg. 1 presents the pseudocode of the proposed ICG clustering phase. The proposed algorithm uses a greedy approach to form the clusters. The inputs to the clustering algorithm are: (i) the ICG generated in the ICG Construction Phase; (ii) a sorted vertex list, where nodes are sorted by their degrees in ICG; (iii) a capacity budget, denoting the number of lines of item embeddings/psums allowed in the cache space. We maintain an active list of vertices that are not clustered and update this list as the algorithm progresses. The algorithm loops over all active vertices and attempts to greedily form new clusters. Within each loop, the largest degree vertex that is active is chosen as an anchor node and is passed to FORMCLUSTER() to form a cluster of an arbitrary size. Upon forming a cluster, occupied\_space is updated. For each cluster, the algorithm saves all combinations of its constituent items, taking an additional size of 2<sup>cluster\_size</sup> - 1 - cluster\_size compared to originally stored item embeddings. The algorithm terminates when the occupied\_space reaches the capacity budget. We now detail how to form clusters.

**Forming a cluster.** Alg. 2 presents the pseudocode for forming individual clusters. The function receives four inputs: (a) the ICG, (b) anchor\_node—a starting node from which we attempt to form a cluster, (c) active list of nodes that are not yet clustered; (d) remaining cache capacity. Given an anchor node, all its neighbors that are part of the active list become the candidates to be added to the cluster. We use a cost-benefit model to estimate the cost efficiency obtained by including a new node in the cluster. To select the best candidate to add to the existing cluster, we compute the estimated benefit of each of the candidates to the cluster, and admit the node that yields the maximum expected benefit. This algorithm

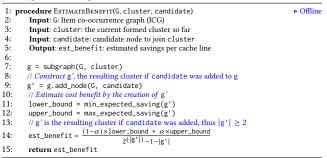

# **Algorithm 2** Pseudocode for an algorithm to form a new cluster under a capacity budget.

| 1: p<br>2: | rocedure FORMCLUSTER(g, anchor_node, active_list)                                                                        | ▷ Offline |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----------|

| 3:         | Input: G: Item co-occurrence graph (ICG)                                                                                 |           |

| 3.<br>4:   | <pre>Input: anchor_node: The node selected to create the cluster<br/>Input: active_list: List of unclustered nodes</pre> |           |

| 4:<br>5:   | Input: remaining_capacity: Remaining memory within the cache space                                                       |           |

| 5.<br>6:   | Output: cluster: Formed cluster containing anchor_node                                                                   |           |

| 7:         | Constant: MAX_CLUSTER_SIZE: Maximum size of any cluster                                                                  |           |

| 8:         | Constant, MAX_CEOSTER_SIZE, Maximum size of any cluster                                                                  |           |

| 9:         | <pre>candidates = {anchor_node}</pre>                                                                                    |           |

| 10:        | best_candidate = anchor_node                                                                                             |           |

| 11:        | current benefit = 0                                                                                                      |           |

| 12:        | while true do                                                                                                            |           |

| 13:        | cluster.append(best_candidate)                                                                                           |           |

| 14:        | candidates.remove(best_candidate)                                                                                        |           |

| 15:        | active_list.erase(best_candidate)                                                                                        |           |

| 16:        | // Potential candidates while inducting the next node into cluster                                                       |           |

| 17:        | candidates.add(active_list ∩ neigh(best_candidate))                                                                      |           |

| 18:        | best_candidate = -1                                                                                                      |           |

| 19:        | current_benefit *= tolerance_factor                                                                                      |           |

| 20:        | <pre>if cluster.size() &gt;= MAX_CLUSTER_SIZE then</pre>                                                                 |           |

| 21:        | break                                                                                                                    |           |

| 22:        | if 2 <sup>cluster.size()+1</sup> - 1 >= remaining_memory then                                                            |           |

| 23:        | break                                                                                                                    |           |

| 24:        | for all candidate $\in$ candidates do                                                                                    |           |

| 25:        | // Estimate benefit of adding the candidate to the cluster                                                               |           |

| 26:        | <pre>est_benefit = EstIMATEBENEFIT(G, cluster, candidate)</pre>                                                          |           |

| 27:        | <pre>if est_benefit &gt; current_benefit then</pre>                                                                      |           |

| 28:        | <pre>current_benefit = est_benefit</pre>                                                                                 |           |

| 29:        | <pre>best_candidate = candidate</pre>                                                                                    |           |

| 30:        | <pre>if best_candidate &lt; 0 then</pre>                                                                                 |           |

| 31:        | return cluster                                                                                                           |           |

| 32:        | return cluster                                                                                                           |           |

is greedy because it chooses the *next* best node from the candidate set to insert into the clusters. When a new node is admitted to the cluster, it is removed from the candidate set and the active list. For the next iteration, the candidate set is updated to contain the neighbors of all the nodes in the cluster so far that are in the active list. In each round, after determining a new node to join the cluster, we record the total estimated benefit so far. When new candidates are evaluated, they are deemed valid to join the cluster if the cost efficiency yielded by their addition to the cluster is greater than the previous cost efficiency (within a specified tolerance level). This procedure terminates when one of the following criteria is satisfied: (i) no valid candidates are found to add to the cluster based on the estimated benefits; (ii) the cluster size exceeds a maximum cluster limit imposed externally; (iii) the cluster exceeds the total memory budget in the cache space. Finally, the formed cluster is returned.

Cost-benefit model for joining a cluster. The goal of the costbenefit model is to estimate the benefit of admitting a candidate node into a given cluster. Measuring the exact benefit of adding a node to a cluster of items requires going over the entire trace of user accesses to measure the frequency of *all* subsets of items. The resulting complexity would be exponential with the size of the cluster. Therefore, it is prohibitively expensive and unrealistic even for small datasets. The key idea of our approach is to exploit the item co-occurrence graphs to estimate the expected savings of a cluster without explicitly counting the frequency of all combinations. Our estimates rely on inclusion-exclusion rules in combinatorics [10]. This allows us to build lower and upper bounds on the frequency of larger tuples (triplets, quadruplets, and beyond) by only measuring the frequency of pairs (i.e. the number of co-occurrences). These lower and upper bounds on frequencies directly allow us to estimate the lower and upper bounds of the expected bandwidth reduction resulting from caching all subsets of a given cluster.

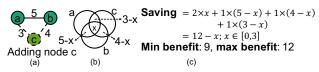

Figure 3: An example demonstrating the cost-benefit model of adding a node to an existing cluster.

We provide an intuitive explanation of our cost-benefit estimation using an example. In Fig. 3, suppose we are provided with a cluster that already contains items a and b, and our goal is to estimate the benefit of adding item c to the cluster. As depicted in Fig. 3(a), suppose items a and b are co-accessed 5 times, items band c are co-accessed 4 times, and items a and c are co-accessed 3 times. However, note that the graph, since it encodes only pairwise relations, does not offer any information on how often all three items are accessed together. We can represent this information in the form of a Venn diagram where (a, b), (b, c), and (c, a) correspond to different sets, as depicted in Fig. 3(b). We assume that the intersection of three sets has x elements. Storing the partial sum of a, b & c, denoted by psum(a, b, c), reduces the number of embedding fetches from 3 to 1 when all these items are accessed together. Storing the partial sums of pairs, on the other hand, would save one embedding fetch if the pair is co-accessed. Based on this knowledge, we can calculate the total savings of caching all pairs and the triplet as shown in Fig. 3(c) as a function of x. Given the number of co-accesses between (a, b) = 5, (b, c) = 4, and (c, a) = 3, the maximum frequency of (a, b, c) could be 3 and the minimum frequency of (a, b, c) could be 0. Therefore, caching all combinations of a, b, and c yields worst-case and best-case savings of 9 and 12, respectively.

Forming a cluster with nodes a, b, and c implies that we cache these embeddings and their partial sums: emb(a), emb(b), emb(c), and additionally psum(a, b), psum(b, c), psum(a, c), and psum(a, b,<math>c), *i.e.*, 4 additional cached partial sums. Consequently, the costbenefit model estimates the maximum and minimum benefit of adding a node c to the cluster of nodes a and b would be 9/4 (min\_expected\_saving in Algorithm 3) and 12/4 (max\_expected \_saving in Algorithm 3). In practice, we observe that the exact benefit of adding a node to a cluster is around the midpoint of the maximum and minimum estimated benefits. We use a linear interpolation factor  $\alpha$  between the lower and upper bounds of the benefit to estimate the cost efficiency of the proposed cluster as shown in Algorithm 3. §B.4 discusses the sensitivity of tuning of this estimation. GRACE uses a graph-based algorithm, which readily applies to multiple embedding tables (shown in §A.3).

#### 4.3 A Walk-Through Example

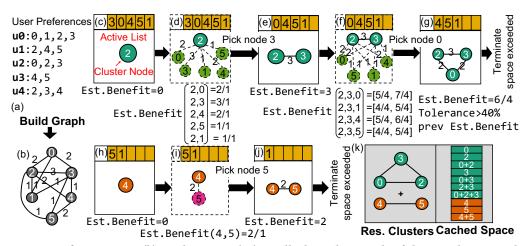

To best understand the proposed algorithms, Fig. 4 shows a walkthrough example of our ICG building and clustering phases. Fig. 4(a) shows the user-item interaction trace, where 5 different users are accessing unique items. In this example, we set the maximum cache capacity to 10 cached items, tolerance factor to 0.4, and  $\alpha$  to 0.5. Note that our algorithms are not restricted to these parameters and can work for any parameter setting, these parameters are chosen for simplicity.

Fig. 4(b) shows the ICG that is formed as a result of shown user preference trace. In this example, the node IDs correspond to items

Figure 4: (a) User-item preference trace, (b) resulting ICG, (c-j) a walk-through example of the ICG clustering algorithm, and (k) resulting clusters and cached embeddings.

# **Algorithm 3** Pseudocode to estimate the cost benefit of a node joining an existing cluster

from 0 to 5. The edge weights of ICG represent the number of times items corresponding to its source and destination nodes are co-accessed. For example, items 2 and 3 are co-accessed by three users, *i.e.*, users 0, 2, and 4, hence, a weight of 3 is assigned to the edge between ICG nodes 2 and 3. This graph is a result of the ICG building phase, the next phase is clustering this graph.

The ICG clustering algorithm starts by assigning all nodes to the active list, and picking the first node to start forming clusters. As shown in Fig. 4(b), because node 2 has the highest degree (*i.e.*, item 2 is the most popular), the first node that starts building clusters is node 2 (Fig. 4(c)). Based on line 24 of Algorithm 2, all the neighbors of node 2 from the active list are picked to estimate the benefit–per–cached–space of adding them to an existing cluster. Based on the ICG connectivity, node 3 has the best estimated benefit of 3/1 for getting added to the cluster. Therefore, our algorithm picks node 3, and forms a cluster of nodes 2 and 3. Note that this cluster takes 3 cache spaces, which is less than the cache budget of 10. Therefore, this algorithm continues and it attempts to find new nodes to add to the same cluster.

As shown in Fig. 4(f), the cluster expansion continues by examining the neighbors of ICG nodes 2 and 3 to the existing cluster. Using nodes 0, 1, 4, and 5, the algorithm calculates the cost of adding each of these nodes to an existing cluster of nodes 2 and 3. The figure shows the range of benefits calculated by our algorithm, and using an  $\alpha$  of 0.5, node 0 has the highest estimated benefit of 6 / 4 (the denominator of 4 is because the cluster of three nodes would consume 4 additional caching locations). Because this benefit is within a tolerance limit of the previously estimated benefit (*i.e.*, 6 / 4 > 0.4 × 3), node 0 is added to the cluster. At this point, 7 out of 10 cache spaces are claimed, and adding any more nodes to the cluster would result in more than 10 cache spaces. Therefore, this clustering algorithm terminates, and it picks up a new node 4 from the active list to form a fresh cluster. The result of this iteration of clustering is a 2-node cluster with nodes 4 and 5.

Fig. 4(k) shows the result of this clustering algorithm, where two clusters are formed with 2 and 3 nodes. It also shows the consumption of cache space taken by these two clusters. Here, 0+2means the partial sum of items 0 and 2. Of note are two important details: (i) clusters can be of **different** sizes (size of 2 and 3 in this example); (ii) the partial sums of **all combinations** of items in a cluster are cached. The cache layout is carefully tailored to compute addresses easily (detailed in §5.3). In practice, the cache space budget is much higher, and this algorithm forms several clusters of different sizes.

#### 4.4 Overhead Analysis

**Complexity Analysis.** Denote the number of users by *m*, and the average length of item interactions per user by *p*. The complexity of ICG construction (Algorithm 4) is  $O(mp^2)$ . Let *n* be the number of nodes (items) in ICG, *d* be the average degree per node, and *k* be the average size of a cluster. The complexity of a single evaluation of the cost model is  $O(k^2)$ . In Algorithm 2, the while(true) loop is iterated *k* times; each iteration makes *d* calls to the ESTIMATEBEN-EFIT() function (Algorithm 3). Therefore the overall complexity of FORMCLUSTER() is  $O(dk^3)$ , executed  $\frac{n}{k}$  times. Thus, the overall complexity of clustering the ICG is  $O(ndk^2)$ .

We highlight the following merits of our algorithmic framework: (i) the ICG construction phase is *linear* in the number of users; (ii) the clustering algorithm is *linear* in the number of items. This allows our approach to scale to a large number of users and items. The ICG clustering complexity is quadratic to k. Our evaluation shows that k goes up to 8 for the best DLRM performance, making the clustering algorithm practical.

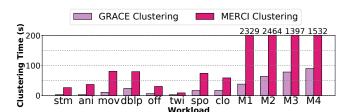

Figure 5: Clustering time comparison of **GRACE** and MERCI using a 128-thread implementation among different datasets.

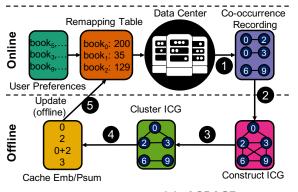

Figure 6: Usage model of GRACE.

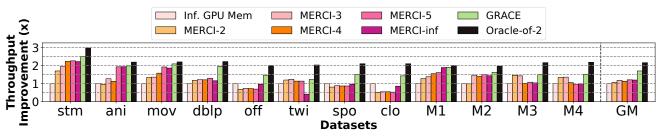

**Runtime Analysis.** To evaluate the runtime overhead of GRACE clustering algorithm, we implement a parallel version of this algorithm in C++ using OpenMP. To best match our estimation to a data center deployment scenario, we run this clustering algorithm on a high-end server-grade CPU discussed in §6.2. Using a 128-thread implementation, Fig. 5 compares the clustering speeds of GRACE and MERCI. GRACE achieves 8.3× faster clustering on average among all datasets, and 26.6× among the mixed datasets that have a larger number of items. *This shows that the GRACE algorithmic framework meets one of its key goals, i.e., designing a practical and scalable algorithm.* With the low-cost scalable clustering algorithm, GRACE can adapt to frequent user-item preference behavior changes even at an update frequency of hours.

#### **5 GRACE SYSTEM DESIGN**

The algorithmic framework of GRACE is generic and can apply to various types of memory systems. Here, we consider the use case of a CPU-GPU heterogeneous system and present GRACE system design. Our system modeling choice is motivated by the fact that this type of system is widely adopted in today's data centers that execute DLRMs [25, 45, 63, 76].

#### 5.1 Usage Model

Fig. 6 depicts a high-level overview of the usage model of GRACE. It consists of online profiling of user-item interactions, offline ICG construction, clustering, and populating the cache space with partial sums of clusters. GRACE is immediately deployable on commodity hardware platforms. In what follows, we detail the GRACE online and offline components.

**Online profiling.** While running DLRM inference in a data center, GRACE samples a subset of users, and records their item interactions. Specifically, it records which items are accessed together (*i.e.*, pairwise item co-occurrence recording as depicted in Fig. 6) and lazily updates the ICG. The lazy nature of graph updates means

H. Ye, S. Vedula, Y. Chen, Y. Yang, A. Bronstein, R. Dreslinski, T. Mudge, and N. Talati

that the incoming edges to the graph can be buffered and processed at a later point in time. This ensures that the recording phase does not interfere with the performance of the ongoing DLRM inference.

Offline analysis. As presented in Fig. 6, GRACE collects the edges recorded during the online profiling phase, and constructs the ICG offline. The constructed ICG is then clustered to find frequently accessed item combinations as discussed in §4. For each cluster, GRACE identifies and fetches the embedding vectors of the constituent nodes, computes psums, and caches embedding vectors and *psums* into the cache space. GRACE generates clusters in decreasing order of expected cost-benefit efficiency, as shown in Algorithm 1. It then stores clusters of *psums* accordingly to the GPU and then the CPU. As shown by prior industrial [63] and academic [1, 34, 48] works, DLRMs employ a remapping table to keep track of cached items. GRACE re-purposes this remapping table to reflect the cached item set. More details on how to filter cached and non-cached accesses, and how to determine the addresses of psums are presented in §5.3. Note that the clustering of ICG and computing/caching psums does not affect DLRM inference latency as they are carried out offline. Using psums does not change the reduction results; GRACE does not affect DLRM inference accuracy.

**Justification of the usage model.** As shown in prior works [50], data center operators typically employ feedback-driven [11] and post-link optimizations [47, 56] to improve the performance of their workloads. In the case of DLRM workload, for example, a data center operator like Meta may profile and record user-item interactions for a week, analyze them offline to create a cache space, and deploy the updated system for inference in subsequent weeks. Several prior works [5, 11, 39–41, 56] have successfully demonstrated that profile-guided techniques, similar to GRACE, are practical and they are deployed in data centers today.

## 5.2 Heterogeneity Awareness

One of the key goals of GRACE is to achieve a **heterogeneous memory-aware** framework that also optimizes for high aggregate memory utilization. To compare, MERCI optimizes for a single metric of maximizing the memory traffic reduction. Large clusters formed by MERCI, while yielding a greater bandwidth reduction, prevent most embeddings from being stored in a capacity-limited cache space. In that case, the main memory becomes the throttling bottleneck in processing user requests, and it prevents a high heterogeneous memory utilization.

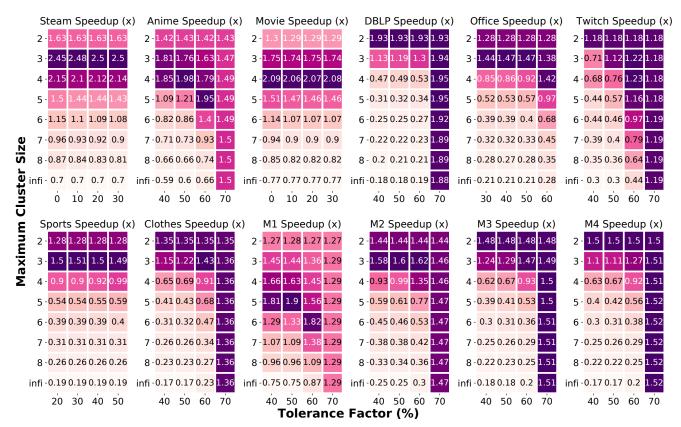

To combat this, GRACE can be tuned to form appropriately sized clusters to store a greater diversity of item embeddings and combinations to effectively use the cache space. GRACE uses the parameters MAX\_CLUSTER\_SIZE and tolerance\_factor discussed in Algorithm 1 to navigate the complex trade-off space of memory traffic reduction and balance of the heterogeneous memory bandwidth. To be able to apply GRACE to arbitrary input and get the best speedup, GRACE uses a lightweight decision engine to find the best parameter given dataset characteristics. We use three features from the dataset input: *number of items, average pooling factor*, and *average node degree in ICG* to train the decision engine. We use the decision tree implementation from scikit-learn [60] library and use an optimized CART (Classification and Regression Trees) algorithm. The decision engine can pick the optimal or near-optimal combination of maximum cluster size and tolerance without exhaustively

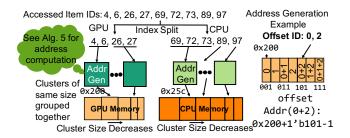

Figure 7: Example of GRACE cache space layout and address generation. User access IDs are compared with the starting address of each unique length of the cluster group to find any clustered accesses. Those clustered accesses have their partial sum ready in the memory, the address of which can be directly computed based on their IDs.

experimenting with all possible combinations. The decision engine accuracy performance is detailed in Appendix §C with a full sweep of different maximum cluster sizes and tolerance combinations shown in Fig. 20.

#### 5.3 Address Generation

As detailed in §5.1, GRACE constructs and clusters an ICG, and stores psums into a cache space offline. To efficiently use these psums to improve end-to-end performance, it is crucial to design an efficient cache address computation logic. To this end, we propose a cache data layout and corresponding address generation technique for efficient GRACE system design. The goal of our designed combined cache data layout and address generation is to compute the address based on the accessed user index at an extremely low cost in software. Fig. 7 shows the proposed layout of cached data, where the clusters of the same sizes are grouped together and laid out adjacent to one another in the address space. Notably, GRACE employs a software-managed cache space to avoid hardware additions to commercial hardware platforms. Because software injects cache lines offline, it does not disturb the ongoing inference cycles. To understand cache layout and address generation with a simple example, assume that the largest size cluster is 4 nodes. GRACE first stores all 4-node clusters, then 3-node clusters, and so on. The item IDs are remapped in the order of clusters. Algorithm 5 (see Appendix §A.2) presents the pseudocode for generating redirected addresses. Given the embedding index of the accessed item, the address generation logic can quickly derive whether the index belongs to the CPU or the GPU. The memory location of the cluster, the cluster size, cluster ID, and offset within the cluster are used to determine specific psum addresses (Fig. 7 right). With the above cache layout, the user index only needs to compare with the starting address of each unique length of the cluster group (in practice at most 8 entries) and then compute the address of the embedding vector/partial sum without accessing additional data structures.

#### 5.4 End-To-End System Design

Fig. 7 presents the end-to-end system execution of GRACE. The *psums* are pinned in the CPU and GPU memory using GRACE software. Similar to an earlier work, we execute on a heterogeneous CPU/GPU system [14], and we use 1 GB super pages to avoid any paging overhead. GRACE re-purposes the remapping

table [1, 34, 48, 63] in software to process the incoming user requests of embedding layers. The remapped and sorted indices split the requests to either CPU or GPU. With a software-defined cache space, the item indices can directly translate into the cluster ID and offset within the cluster. Using Alg. 5, the redirected addresses are used to correctly serve the requested indices with *psums* in the heterogeneous memory. The item embedding reduction is then executed on both CPU and GPU simultaneously before the CPU results are sent and reduced with the GPU results (see Fig. 1(b)). Each batch synchronously reduces item embeddings and computes sparse features on GPUs before processing the top MLP layers. The address generation process of the batch of users is overlapped with the item embedding reduction of the previous batch to ensure that address generation is not on the critical path. We show in §7.1 that the latency of address generation is negligible compared to embedding reduction time.

## 6 METHODOLOGY

#### 6.1 Real-World Datasets

We use a variety of datasets from different web service vendors, shown in Table 1. We choose datasets of different sizes and average pooling factors. The average pooling factor of a dataset is defined as the number of items, on average, reduced by each user to compute sparse embeddings.

| Category | Dataset Name             | Avg. Pool. Factor | #Items    |

|----------|--------------------------|-------------------|-----------|

|          | Steam (stm) [36, 59, 71] | 71.8              | 10,978    |

| Small    | Anime (ani) [2]          | 106.3             | 11,200    |

|          | MovieLens20M (mov) [27]  | 144.4             | 26,744    |

|          | DBLP (dblp) [62]         | 61.8              | 540,459   |

| Medium   | AmazonOffices (off) [29] | 64.0              | 598,943   |

|          | Twitch (twi) [61]        | 30.5              | 739,991   |

| Landa    | AmazonSports (spo) [29]  | 96.1              | 1,505,707 |

| Large    | AmazonClothes (clo) [29] | 82.0              | 2,345,346 |

#### Table 1: Real-world datasets from web service vendors.

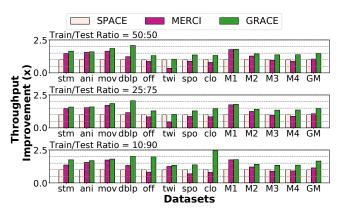

In addition to evaluating uniform datasets, we also present an evaluation with a mixture of the datasets to model the real-world recommendation system that has multiple embedding tables of different sizes and properties. Table 2 lists the mix of our datasets. For each dataset, we split by 50:50 ratio to profile the behavior and estimate inference performance (we sweep the training/test ratio in B.3). We use the embedding dimension of 1024 and the user batch size of 1024. For end-to-end speedup analysis, we use DLRM models in Table 3.

| Ta | ble | 2: | Ex | peri | men | ted | mix | ture | of | datasets. |

|----|-----|----|----|------|-----|-----|-----|------|----|-----------|

|----|-----|----|----|------|-----|-----|-----|------|----|-----------|

| Dataset Name | Mixture of Dataset | Classes  |

|--------------|--------------------|----------|

| M1           | twi-mov-ani-stm    | 1M+3S    |

| M2           | clo-off-dblp-ani   | 1L+2M+1S |

| M3           | spo-off-dblp-twi   | 1L+3M    |

| M4           | clo-spo-off-dblp   | 2L+2M    |

## 6.2 System Configuration

For sampled user traces, we build ICG and form clusters using the GAPBS [6] framework. We deploy all the inference tasks on a high-end server and measure the performance. For a heterogeneous memory system deployment, we use an Intel Xeon Platinum 8380 CPU with 80 physical cores and 512GB 32-channel DDR4-3200 main memory as the CPU host. We use NVIDIA A40 with 48 GB GDDR6

H. Ye, S. Vedula, Y. Chen, Y. Yang, A. Bronstein, R. Dreslinski, T. Mudge, and N. Talati

memory as the GPU device. The embedding table reduction operation executed on CPU uses AVX-512 instructions, same as [25]. We use OpenMP to parallelize multiple embedding-reducing operations from different users and we verified the full utilization of CPU bandwidth. We also verified the correctness of the embedding layer functionality since GRACE does not alter any reducing results of embedding layer operations.

While GRACE presents a generic algorithmic and system design framework to improve DLRM inference throughput, we evaluate GRACE and prior works [34, 48] using a heterogeneous CPU-GPU system for a fair comparison. GRACE, however, can be generalized and adapted to any heterogeneous memory configuration with a main memory and cache space.

Table 3: DLRM models for end-to-end performance analysis.

| DLRM Model   | Bottom MLP       | Top MLP   | Num. of table |

|--------------|------------------|-----------|---------------|

| RM1 [24, 26] | 128-64-32        | 256-64-1  | 8             |

| RM2 [24, 26] | 256-128-64       | 128-64-1  | 32            |

| RM3 [24, 26] | 2560-1024-256-32 | 512-256-1 | 10            |

| RM4 [78]     | -                | 200-80-2  | 3             |

#### 6.3 State-of-the-Art Baselines

**Infinite GPU memory.** This solution models an infinite GPU memory capacity that can host full embedding tables in GPU memory, regardless of size. It does not store any *psums*.

**CPU only.** This baseline models hosting full embedding tables in the CPU memory. We use all 80 cores for executing DLRM.

**Off-the-shelf clustering techniques.** We use the state-of-theart graph clustering algorithm Metis [46] that can apply to ICG clustering. Metis uses a recursive k-way multi-level graph partitioning algorithm to form clusters.

**FAE** [1]. We model an ideal performance of FAE that places a subset of highly accessed item embedding vectors in a cache space. There is no memory traffic reduction mechanism in FAE. To report the optimal performance of FAE, we sweep every possible cut-off frequency value for each dataset separately. The performance is also an indicator of the upper bound performance of utilizing the heterogeneous memory without reducing the memory traffic.

**SPACE** [34]. SPACE is a state-of-the-art recommendation system inference framework that uses static analysis of user preferences to find popular items. It significantly outperforms other hybrid DRAM management frameworks [15, 16, 65]. SPACE caches the single popular items and an exhaustive set of combinations of two items in GPU memory. SPACE offers a rich design space in terms of the fraction of single versus partial embedding sums stored in the cache space. We report the results for the best-performing parameter setting by extensively sweeping the value of this fraction.

**MERCI** [48]. MERCI is a state-of-the-art framework to generate clusters of *psums* to reduce the memory traffic. Although MERCI is proposed for a DIMM-only system, we assume that their clusters of *psums* are stored in GPU memory. We use the open-source implementation [3] from authors. Additionally, we navigate the subgroup size-performance trade-off in MERCI to find the best-performing parameters and report the optimal performance numbers.

**Oracle-of-2**. We model an oracle with a *psum of 2* that can find partial sums of **any** 2 item embeddings. While an oracle-of-3 or larger is possible in theory, we choose the oracle-of-2 because it

provides a reasonable reduction factor roofline to compare the modeled systems. For this oracle, we assume that it perfectly balances the memory bandwidth in a heterogeneous memory system (§6.2).

## 7 EVALUATION RESULTS

#### 7.1 Performance Analysis

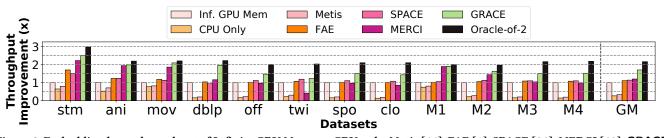

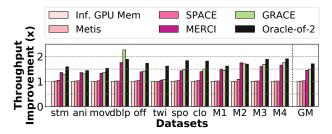

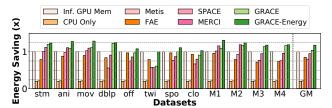

GRACE vs. prior works. Fig. 8 compares the embedding layer throughput of GRACE with CPU only, Metis clustering [46], FAE [1], SPACE [34], MERCI [48], and an Oracle-of-2 normalized to an infinite GPU memory solution. GRACE and prior works use extra memory capacity to store embedding vectors/partial sums that is equal to 1× the size of the original embedding table. The figure shows that CPU slows down the execution by 3.7× compared to the infinite GPU memory baseline. This is because the compute throughput and peak memory bandwidth of GPU are much higher than CPU. FAE achieves 1.1× better performance than the baseline. We sweep every possible cut-off frequency for each dataset separately and report the best performance. FAE only marginally improves the performance of the baseline because of no memory traffic reduction. Moreover, the figure shows that, on average, the off-the-shelf clustering algorithm (Metis) only achieves 0.34× the baseline performance. The slowdown is attributed to the fact that a generic clustering algorithm does not contribute to partial sum reductions or heterogeneous memory utilization effectively. This clearly motivates the design of a novel ICG clustering algorithm to best accelerate DLRM inference.

Fig. 8 shows that GRACE outperforms SPACE and MERCI by 1.5× and 1.4×, on average. As discussed in §6.3, we report the best performance of SPACE and MERCI based on extensive parameter tuning. This significant performance improvement is attributed to the GRACE algorithm and system design that (a) finds popular item combinations of arbitrary lengths in a scalable fashion, and (b) is memory heterogeneity aware by effectively navigating the trade-off of expanding the partial sum sizes or storing more item embeddings. GRACE effectively bridges the performance gap between prior works and oracle-of-2 by 52.1%. The performance of SPACE and MERCI are limited due to limited reduction in memory traffic and memory heterogeneity unawareness, respectively. This, in turn, shows that GRACE finds high-quality popular item combinations to effectively reduce the memory traffic, and rejects over-sized clusters to prevent DRAM throttling. This optimizes the collective heterogeneous memory bandwidth. Interestingly, we find that GRACE performance is positively correlated with the average ICG node degree. The bestperforming datasets over prior works (stm, ani, mov, and M1) have the highest ICG average node degrees of (1405, 1148, 2107, and 900).

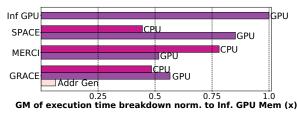

**Heterogeneous memory time split.** To further understand the performance of different baselines, Fig. 9 shows the time split for the embedding reduction in CPU and GPU memories. Ideally, a system that splits memory traffic to balance the execution times spent on CPU and GPU can achieve high throughput.

SPACE moderately reduces the GPU execution time by 15% compared to a system with infinite GPU memory, which determines the overall throughput of SPACE. Because GPU has a much higher memory bandwidth available compared to CPU, a moderate memory traffic redirected from GPU to CPU memory will result in a significant increase in CPU memory time. *This result underscores*

Figure 8: Embedding layer throughput of Infinite GPU Memory, CPU only, Metis [46], FAE [1], SPACE [34], MERCI [48], GRACE and Oracle-of-2 normalized to Infinite GPU Memory. All works use 1× additional table capacity to store partial sums.

Figure 9: Embedding layer execution time breakdown across CPU and GPU memory, averaged among all datasets, normalized to the infinite GPU memory execution time. Ideally, the memory system achieves a balanced execution.

the value of achieving high memory traffic reduction to speed up the workload. MERCI performance, on the other hand, is determined by the embedding reduction time on the CPU. This is because reducing memory traffic is the sole design objective of MERCI, which leads to large cluster sizes. In a real-world heterogeneous memory setting, this leads to spilling of many embedding psums to CPU memory, inadvertently increasing its execution time.

The GRACE design effectively navigates the complex design space of reducing memory traffic by storing large clusters versus distributing more memory traffic to the heterogeneous memory system. Fig. 9 shows that GRACE achieves a near-perfect execution time split between CPU and GPU to maximize overall application throughput. The address generation time is shown separately because it refers to the latency to compute memory addresses and distribute psums/item embedding requests to CPU and GPU. This is off the critical path of the embedding reduction latency as it can be pipelined with the previous batch reduction. Finally, the figure also shows that the address computation time is negligible (6%) compared to the time to load and reduce item embeddings. The GRACE runtime system thus can fully hide address computation latency by overlapping it with the embedding reduction of the previous batch.

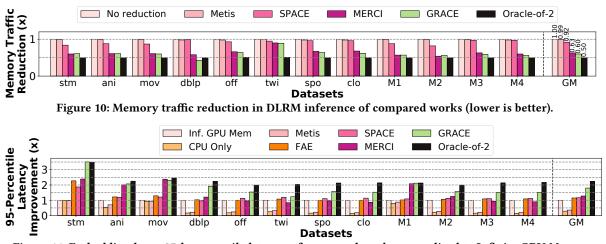

**Memory traffic reduction.** Fig. 10 shows the comparison among different baselines. The oracle-of-2 achieves a 50% reduction in the memory traffic as it stores psums of all two-item embeddings (not practical). SPACE only reduces memory traffic by 9% because it stores partial sums of two item combinations of a very small subset of items. MERCI and GRACE can reduce memory traffic by 37% and 40%. Note that dblp has a memory reduction factor of 2.3× for GRACE, which is higher than the modeled oracle-of-2. Although MERCI inspects full training traces to generate optimal clusters, the high complexity of such inspection forces the algorithm to break into sub-groups. During this process, co-accesses between different

sub-groups are ignored and MERCI may miss the opportunity to analyze a global set of co-accessed items. GRACE, on the other hand, does not have such constraints and the ICG captures accesses of all items. This result also shows that even in a traditional DIMMonly memory system, GRACE results in higher memory reduction and outperforms MERCI.

**Tail latency comparison.** Fig. 11 shows the 95th percentile latency of processed batches of compared works, normalized to the infinite GPU memory solution. The figure shows that GRACE consistently outperforms the state-of-the-art works in terms of tail latency as well as throughput. Specifically, GRACE improves SPACE by 1.54× and MERCI by 1.41×.

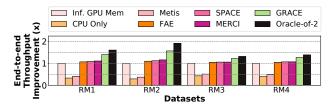

**End-to-end DLRM performance.** By speeding up the embedding reduction phase, GRACE also significantly improves the endto-end throughput of DLRM. Fig. 12 shows that GRACE offers a significant end-to-end performance improvement of 1.6× over infinite GPU memory on embedding-heavy models such as RM2. In MLP-heavy models such as RM3, GRACE achieves 1.2× speedup, outperforming prior works. DLRMs are executed at a population scale. Even a single percent performance improvement in data center applications leads to a significant reduction in Total Cost of Ownership (TCO) and global carbon footprint [5, 35]. DLRMs consume more than 60% of AI inference cycles [26]. Fig. 12 shows that GRACE provides significant end-to-end performance improvement of 1.2-1.6× compared to MERCI and offers a low-cost solution, obviating intrusive hardware modifications. Therefore, GRACE can be immediately adopted in today's data centers.

Understanding the improvements over MERCI. MERCI is the state-of-the-art framework aiming at memory traffic reduction in DLRM. Interestingly, we observe that GRACE outperforms MERCI in both memory traffic reduction and end-to-end throughput. The reason behind this improvement is twofold. 1) GRACE has a global view of user-item interactions, irrespective of the dataset size. This is enabled by our novel graph construction that allows scalable analysis at a global dataset scale. §4.4 shows that GRACE analysis scales from both algorithmic complexity and runtime standpoints. MERCI's analysis, on the other hand, has a fundamental limitation that it operates at a sub-group level and fails to capture a global view of user-item interactions due to scalability issues. 2) While MERCI only aims to improve memory traffic reduction, the proposed GRACE algorithm is memory heterogeneity-aware. GRACE not only improves memory traffic reduction, but also results in a balanced memory traffic distribution further improving end-to-end throughput.

Figure 11: Embedding layer 95th percentile latency of compared works normalized to Infinite GPU Memory.

Figure 12: End-to-end DLRM inference performance of compared works normalized to Infinite GPU Memory.

Figure 13: Embedding layer throughput comparison in a homogeneous GPU memory platform.

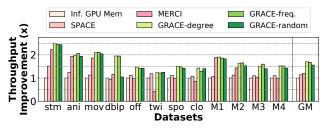

**Comparison using additional hardware configurations.** GRACE algorithm-system co-design is agnostic to any specific hardware configuration. While a CPU-GPU platform represents a baseline modeling for a majority of our evaluation, next, we show the performance of GRACE using two other hardware platforms.

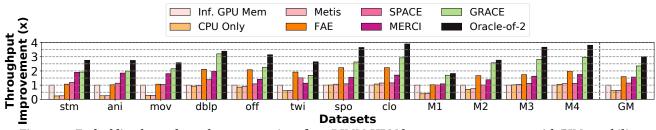

First, we compare the performance of various baselines on a homogeneous GPU memory in Fig. 13. This experiment assumes an infinite GPU memory. Because this platform does not have heterogeneous memory, the performance is directly correlated with memory traffic reduction. GRACE outperforms MERCI marginally by 5%. This corroborates with the traffic reduction ratio in Fig. 10. Furthermore, GRACE significantly outperforms Metis and SPACE due to improved memory traffic reduction.

Second, Fig. 14 shows the embedding layer throughput improvement on a system having hybrid DIMM-HBM memory with Process-In-Memory (PIM) technology (evaluation similar to SPACE [34]). We simulate the embedding reduction operations in PIM using a trace-based simulation methodology in Ramulator [42]. The modeled DRAM consists of 8 DDR4-3200 channels and 2 stacks of bandwidth-optimized cache space of HBM2 (specifications adopted from [53, 55]). Fig. 14 shows an interesting trend that FAE outperforms SPACE. This shows that heterogeneous memory awareness is increasingly important when the bandwidth capability varies across different platforms. The figure also shows that the memory heterogeneity-aware design of GRACE can adapt to different technological parameters, and consistently offer the best performance compared to the state-of-the-art. By optimizing memory traffic reduction and distribution, GRACE outperforms MERCI by 1.5×.

Table 4: Absolute throughput numbers (*i.e.*, #batches processed per second) of an infinite GPU memory baseline.

| Dataset    | stm  | ani  | mov | dblp | off  | twi  |

|------------|------|------|-----|------|------|------|

| Throughput | 976  | 1125 | 668 | 1594 | 2787 | 4965 |

| Dataset    | spo  | clo  | M1  | M2   | M3   | M4   |

| Throughput | 1924 | 2332 | 361 | 492  | 667  | 583  |

Absolute performance numbers. To enable better reproducibility of results and future comparison with GRACE, Table 4 shows the absolute throughput numbers of an infinite GPU memory baseline as shown in Fig. 8. This result is obtained by running a full embedding layer on the GPU platform (§6.2). The reported absolute numbers are of the same order as a recent industrial work Deep-RecSys [24] (our baselines are more optimistic than DeepRecSys as our embedding layer execution baseline is natively optimized using CUDA/C++ compared to PyTorch). All other absolute numbers reported by our compared works can be inferred by scaling the absolute numbers with speedups shown in the figures.

#### 7.2 Sensitivity Analysis

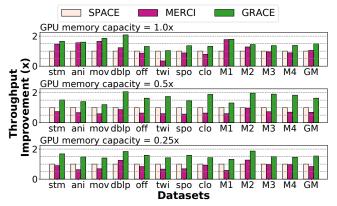

**GPU memory capacity.** In practice, the capacity budget for the high bandwidth memory can be less than  $1.0\times$  because of the capacity-limited GPU memory and large embedding table sizes. Multiple embedding tables also share the GPU memory capacity resources. To measure the effectiveness of GRACE in a more constrained environment, we sweep the allowed cache space capacity to  $0.5 \times$  and  $0.25 \times$  embedding table size. Fig. 15 its effect on embedding reduction performance. With more constrained cache space,

Figure 14: Embedding layer throughput comparison for a DIMM-HBM heterogeneous memory with PIM capability.

Figure 15: Performance sensitivity of compared works for different GPU memory capacities normalized to SPACE.

MERCI further exacerbates DIMM memory throughput by using the constrained space for storing *psums*. GRACE , however, can adapt to the more constrained space by rejecting clusters at an earlier threshold. GRACE balances the throughput of the heterogeneous memory system. On average, GRACE outperforms SPACE by 1.63× and 1.54× in the tested configurations of constrained cache space.

## 7.3 Additional Results

Extensive experiments and further insights on energy analysis and sensitivity studies are presented in detail in Appendix §B.

## 8 RELATED WORK

**Profiling of recommendation systems** [24, 26] shows that the embedding layer accounts for more than 25% and 80% of the inference latency in the Meta RM1 and RM2 model. These RM models consume more than 60% of Meta's data center AI inference cycles. While using specialized DNN accelerators or employing batched inference can significantly [9, 12, 17, 23, 30–33, 51] improve the DNN layer throughput, the embedding layer performance is still bottle-necked by the memory bandwidth [24, 26, 28, 34, 38, 43, 44, 76].

**Exploiting the embedding table locality.** Analysis of the useritem interactions has been studied in prior works [1, 7, 20, 34, 37, 38, 43, 58, 63, 64, 68, 71, 75], such as reducing the dimension and exploiting the power-law characteristics observed in the embedding table operations. SPACE [34] is the most recent work that exploits both singular hot items and exhaustive combinations of partial sums of two hot items. MERCI [48] captures the most efficient *psums* to reduce the memory traffic. GRACE explores the design space of both memory traffic reduction and heterogeneous memory utilization and GRACE analysis is derived by analyzing real-world service vendors instead of artificially generated distribution [24, 25]. Near memory processing and memory technology for improving embedding table operations. Near memory processing is explored in many prior works [38, 43, 57, 69, 70]. They serve as the heterogeneous memory module and significantly increase the available memory bandwidth. Fafnir [4] uses a tree-like reduction hierarchy among different ranks to improve the reduction efficiency near the memory logic. Other memory technologies have been studied in prior works including SSD (solid-state drive) [67, 73] and NVM (non-volatile memory) [19] to aid the embedding layer operation, which has a dual challenge of large capacity and a high bandwidth requirement. GRACE assumes a hybrid DRAM model and uses GPU memory as a software-managed cache and this algorithm framework can generalize to these new memory technologies.

## 9 CONCLUSION